# **Cronfa - Swansea University Open Access Repository**

| This is an author produced version of a paper | published in: |  |

|-----------------------------------------------|---------------|--|

| IEEE Journal of the Electron Devices Society  |               |  |

|                                               |               |  |

| Cronfa URL for this paper:                    |               |  |

| http://cronfa.swan.ac.uk/Record/cronfa39889   |               |  |

# Paper:

Indalecio, G., Garcia-Loureiro, A., Elmessary, M., Kalna, K. & Seoane, N. (2018). Spatial Sensitivity of Silicon GAA Nanowire FETs under Line Edge Roughness Variations. *IEEE Journal of the Electron Devices Society*, 1-1. http://dx.doi.org/10.1109/JEDS.2018.2828504

This item is brought to you by Swansea University. Any person downloading material is agreeing to abide by the terms of the repository licence. Copies of full text items may be used or reproduced in any format or medium, without prior permission for personal research or study, educational or non-commercial purposes only. The copyright for any work remains with the original author unless otherwise specified. The full-text must not be sold in any format or medium without the formal permission of the copyright holder.

Permission for multiple reproductions should be obtained from the original author.

Authors are personally responsible for adhering to copyright and publisher restrictions when uploading content to the repository.

http://www.swansea.ac.uk/library/researchsupport/ris-support/

# Spatial Sensitivity of Silicon GAA Nanowire FETs under Line Edge Roughness Variations

Guillermo Indalecio, Antonio J. García-Loureiro, *Member, IEEE*, Muhammad A. Elmessary, Karol Kalna, *Senior Member, IEEE*, and Natalia Seoane

Abstract-Standard analysis of variability sources in nanodevices lacks information about the spatial influence of the variability. However this spatial information is paramount for the industry and academia to improve the design of variabilityresistant architectures. A recently developed technique, the Fluctuation Sensitivity Map (FSM) is used to analyse the spatial effect of the Line Edge Roughness (LER) variability in key figures-ofmerit (FoM) in silicon Gate-All-Around (GAA) nanowire (NW) FETs. This technique gives insight about the local sensitivity identifying the regions inducing the strongest variability into the FoM. We analyse both 22 nm and 10 nm gate length GAA NW FETs affected by the LER with different amplitudes (0.6, 0.7, 0.85 nm) and correlation lengths (10, 20 nm) using in-house 3D quantum-corrected drift-diffusion simulation tool calibrated against experimental or Monte Carlo data. The FSM finds that the gate is the most sensitive region to LER deformations. We demonstrate that the specific location of the deformation inside the gate plays an important role in the performance and that the effect of the location is also dependent on the FoM analysed. Moreover, there is a negligible impact on the device performance if the LER deformation occurs in the source or drain region.

Index Terms—Si GAA Nanowire; Variability Sources; Line-Edge Roughness (LER); Spatial Sensitivity; Density Gradient (DG) Quantum Corrections.

# I. INTRODUCTION

Gate–all-around (GAA) nanowire (NW) FETs are considered to have excellent electrostatic integrity [1]–[3] which makes them a promising alternative for the 5 nm technology node and beyond according the ITRS [4] and IDRS [5]. Their performance will be negatively affected by variability sources as any other semiconductor device. The nature of NW fabrication process [6] makes challenging to eliminate the effect of metal gate granularity (MGG), random dopants (RD), and line edge roughness (LER), which are recognised to be the major variability sources affecting nanoscale multi-gate transistors [7]–[11].

To assess the impact that different sources of variability have on the device performance [12], simulations of several hundreds or thousands of microscopically different configurations are required with corresponding statistical analysis

- G. Indalecio, A. J. García-Loureiro and N. Seoane are with the Centro Singular de Investigación en Tecnoloxías da Información, University of Santiago de Compostela, 15782 Santiago de Compostela, Spain (e-mail: guillermo.indalecio@usc.es).

- G. Indalecio is also with Institute for Microelectronics, TU Wien, 1060, Vienna, Austria.

- M. A. Elmessary and K. Kalna are with the Nanoelectronic Devices Computational Group, Swansea University, Swansea, Wales, SA1 8EN, U.K. (e-mail:k.kalna@swansea.ac.uk).

- M. A. Elmessary is also with Engineering Math & Physics Department, Faculty of Engineering, Mansoura University, Mansoura 35516, Egypt

of the resulting data [13]. The most common approach to perform this analysis is via the standard deviation of the figures of merit (FoM). However, the standard techniques that analyse variability effects do not provide an insight into the effect that the spatial location of the variation has on the device performance. Since conventional statistical studies do not account for the local effects of a variability source, the feedback they can provide to the industry is limited. To tackle this issue, the Impedance Field Method [14] was presented to understand the effect of small perturbations in the device (as long as these perturbations are small enough) for RD variability in MOSFETs. Another approach [15] analysed the impact of the dopant positions along the device, again for the RD variations, obtaining a measure of how sensitive different parts of the device are.

In this work, we introduce a technique, the Fluctuation Sensitivity Map (FSM), which provides a deeper understanding of how LER variability affects state-of-the-art Silicon GAA NWs. This technique was already successfully demonstrated for FinFET MGG variations [16], presenting an characterisation of the device sensitivity to the metal grains in the gate. In this approach, we are analysing how the placement and the type of LER deformations affect the device FoM. This data will be useful to improve the design of more reliable GAA NWs beyond the analysis that was previously done using mainly statistical measures.

The structure of this article is as follows. Section II presents the device under study and the simulation approach. Section III describes the FSM technique, shows how it is calculated, and gives results for 22 nm and 10 nm gate length GAA NW FETs. Section IV presents the predictive capability of the technique. Conclusions are drawn up in Section V.

### II. DEVICE STRUCTURE AND SIMULATION METHODOLOGY

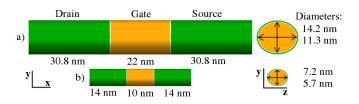

The effect of the LER has been studied in two Si GAA NW FETs (shown in Fig. 1) with gate lengths of 22 nm and 10 nm representative of the 14 nm and 5 nm technology nodes, respectively. The 22 nm gate length device designed from a fabricated NW FET [17] has an elliptical cross–section with a shorter/longer diameter of 11.3/14.2 nm, resulting in an effective diameter ( $D_{ef}$ ) of 12.8 nm. The EOT is 1.5 nm and the length of the source and drain ( $L_{S/D}$ ) regions is 30.8 nm. The 10 nm gate length NW FET has been properly scaled from the 22 nm gate length structure following the ITRS specifications. The shorter/longer diameter of the elliptical cross–section are 5.7/7.2 nm, which makes a  $D_{\rm ef}$  of 6.4 nm,

the EOT is 0.8 nm and  $L_{S/D}$  is 14.0 nm. Both device structures have Gaussian n-type doping in the S/D with a peak value of  $5 \times 10^{19}$  cm<sup>-3</sup>. The spread  $\sigma$  determines the abruptness of the doping profile and is equal to 7.1 and 3.2 nm for the 22 and 10 nm gate length devices, respectively. In the channel, there is an uniform p-type doping ( $10^{15}$  cm<sup>-3</sup>).

Figure 1. Schematic illustration of the 22 nm gate length GAA NW FET and its 10 nm version, with the same scale, corresponding to 14 nm and 5 nm technology nodes. We set X=0 at the middle of the gate, therefore the S/D contacts are located at both ends of the depicted devices (X= $\pm41.8$  and  $\pm19$  nm for the 22 and 10 nm gate length devices, respectively).

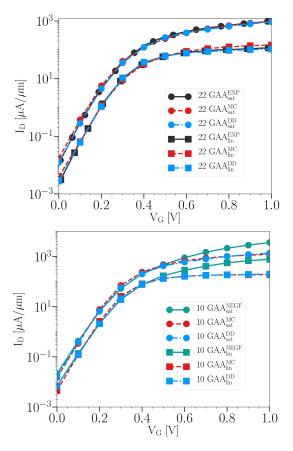

The devices have been modelled using an in-house built 3D finite-element (FE) density-gradient (DG) quantum-corrected drift-diffusion (DD) device simulator [18]. This simulation toolbox has been previously used for variability studies affecting different types of semiconductor devices and variability sources [11], [19], [20]. The FE tetrahedral mesh is able to accurately replicate the experimental elliptical shape of NW FETs. For the 22 nm gate length GAA NW FET, the  $I_D$ – $V_G$  characteristics at both low (0.05 V) and high drain biases (1.0 V) obtained from 3D DD-DG simulations have been calibrated against experimental results [17] and 3D FE Monte Carlo (MC) simulations that include 2D anisotropic Schrödinger equation based quantum corrections (SEQC) along the device channel [11]. For the 10 nm gate length GAA NW FET, since there are no experimental data available, the DD-DG simulations were calibrated to ballistic Non-Equilibrium Green's Function (NEGF) simulations [21] in the sub-threshold region and to SEQC-MC simulations in the onregion (at drain biases of 0.05 V and 0.7 V). The doping profile in the 22 nm gate NW FET has been reverse engineered using  $I_{\mathrm{D}}\text{--}V_{\mathrm{G}}$  characteristics in the sub-threshold region (the region where electrostatic of transistors dominates) as described in detail in [11]. The DD-DG simulations use Caughey and Thomas low-field electron mobility model, which considers doping dependent mobilities [22], together with lateral and perpendicular electric field models [23]. The mobility model parameters included also the saturation velocity (v<sub>sat</sub>) and the perpendicular critical electric field (E<sub>CN</sub>). The work-function (set to 4.56 eV) and the standard deviation in Gaussian doping profile  $(\sigma)$ , have also been employed as calibration parameters. The effective electron masses in the DG approach allow us to mimic the source-to-drain tunnelling, via the electron mass in transport direction (m<sub>x</sub>), and quantum confinement effects [24], collected in Table I. We have obtained an excellent agreement in the  $I_D-V_G$  characteristics for both gate length devices as seen in Fig. 2. Note that, at gate biases larger than 0.5 V, the ballistic NEGF simulations overestimate the drain current since they do not consider scattering events (bottom

Table I Calibration parameters for the 22 and 10 nm gate length Si GAA NW FETs: saturation velocity ( $v_{sat}$ ), perpendicular critical electric field ( $E_{\rm CN}$ ), DG electron mass in the transport direction ( $m_x$ ) and standard deviation for Gaussian doping in the source/drain ( $\sigma_x$ ).

| $L_{G}$                 | 22 nm        |                     | 10 nm               |                         |

|-------------------------|--------------|---------------------|---------------------|-------------------------|

| $V_{\mathrm{D}}$        | 0.05~V       | 1.0~V               | 0.05~V              | 0.7~V                   |

| v <sub>sat</sub> [cm/s] | $1.0 x 10^9$ | $1.0 x 10^9$        | $1.0 x 10^9$        | $1.0 x 10^9$            |

| E <sub>CN</sub> [V/cm]  | $4.0x10^6$   | $1.3 \text{x} 10^5$ | $1.0 \text{x} 10^7$ | $2.5 \mathrm{x} 10^{5}$ |

| $m_{\rm x} \ [m_0]$     | 0.4          | 0.32                | 0.4                 | 0.25                    |

| $\sigma_x$ [nm]         | 7.1          | 7.1                 | 3.2                 | 3.2                     |

figure).

Figure 2.  $I_D$ – $V_G$  characteristics comparing 3D density–gradient quantum–corrected drift–diffusion simulations (DD) against i) experimental data (EXP) [17] and Monte Carlo simulations (MC) for the 22 nm gate length Si GAA NW FET (top figure) and, ii) ballistic Non–Equilibrium Green's Function simulations (NEGF) and Monte Carlo data for the 10 nm gate length Si GAA NW FET (bottom figure).

The LER profile has been applied in the GAA NW FET via the Fourier synthesis method, as described in [19], [25]. LER is defined by two parameters: the correlation length (CL), that characterises the deformation along the x-direction of the device, and the root mean square (RMS) height, that describes the deformation in the y-direction. We have focused the study in uncorrelated LER in which different roughness profiles are applied to the positive and negative y-axis, effectively changing the device width in the x-axis. An example of these

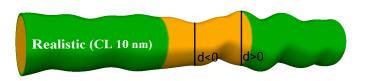

deformations can be seen in Fig. 3. We have analysed two CL values (20 and 10 nm) and three RMS heights (0.85, 0.7 and 0.6 nm) that are consistent with the values observed experimentally [17]. We have then generated sets of 300 realistic LER profiles for each CL and RMS height and applied them to the studied devices. Fig. 3 shows an example of the 22 nm gate length Si GAA NW FET under a LER deformation with a 0.8 nm RMS and a 10 nm CL.

Figure 3. Example of the 22 nm gate length Si GAA NW FET affected by the LER (CL=10 nm and RMS=0.85 nm). Two locations are highlighted either with a positive (d(x)>0) or a negative (d(x)<0) change in width of the device cross-section with respect to the non-deformed device.

### III. CONSTRUCTION OF THE FSM

The Fluctuation Sensitivity Map (FSM) is a tool that represents the spatial sensitivity of the device under a variability source, as previously demonstrated when characterizing the effect of the metal gate granularity [16]. To calculate the FSM, an ensemble of devices affected by some kind of fluctuation due to a variability source has to be simulated. At the end of each simulation, a set of FoMs (e.g.  $I_{\rm off}$ ,  $V_T$ ,  $I_{\rm on}$ ) is extracted, and paired with the corresponding fluctuation. In a LER study, this fluctuation is the deformation that occurs at each location of the device along the x-direction, which can change the device width or its centre. It is important to bear in mind that the FSM will provide the sensitivity of the device to the type of deformation that has been used in the FSM construction.

FSM(x) represents how sensitive a FoM,  $\phi$ , is to the transversal deformation, d(x), present at a x-coordinate, that changes the device width (see Fig. 3), and is given by:

$$FSM(x) = \frac{\partial \phi}{\partial d(x)} \tag{1}$$

Using the obtained FSM(x), we can formulate the following equation for the k-th device affected by the corresponding LER deformation profile,  $d^k(x)$ :

$$\phi^k = FSM(x) \cdot d^k(x) + \phi_0^k, \quad k = 1, ..., N$$

(2)

where  $\phi^k$  is the FoM obtained from the simulation of the k-th device,  $\phi^k_0$  is a fitting parameter and N is the total number of studied devices.

This is the actual set of linear equations that has to be solved. We are running N simulations in total with different deformation profiles, so for each location x, we have N equations to solve. There is not a single value of the FSM(x) that fulfils Eq. (2), so we solve a least squares problem instead to obtain a value for FSM(x). Note that since we are using a discretized mesh, with P elements in the x-direction, we have a set of  $N \times P$  equations to be solved. N and P have to be as large as possible to account for different deformations

along the device, in our case, N=300 and P=1670 for this particular device. This FSM(x) is presented in the following section for different scenarios.

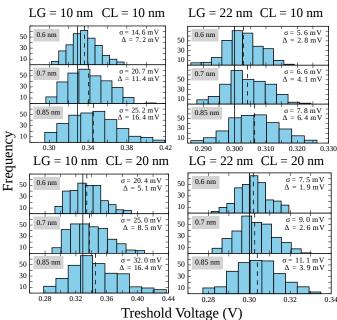

# A. FSM generated using realistic LER profiles

Figure 4. Distribution of  $V_T$  due to LER variability for the 22 and 10 nm gate length Si GAA NW FETs at a low drain bias of 0.05 V as a function of the CL (10, 20 nm) and the RMS height (0.6, 0.7, 0.85 nm as shown in the grey boxes). The standard deviation ( $\sigma$ ) and mean value  $\langle V_T \rangle$  (dashed line) of the distribution are indicated together with the  $V_T$  of the ideal device  $V_{T_{ideal}}$  (full lines) and the  $V_T$  shift  $\Delta = \langle V_T \rangle - V_{T_{ideal}}$ .

Fig. 4 shows the distribution of  $V_T$  due to LER variability in the 22 and 10 nm gate length Si GAA NW FETs at a  $V_D = 0.05 \text{ V}$  as a function of the CL and the RMS height. The standard deviation ( $\sigma$ ) and mean value  $\langle V_{\rm T} \rangle$  (see dashed lines) of the distributions are also shown, together with the  $V_{\rm T}$  of the ideal, not deformed device  $V_{T_{ideal}}$  (see full lines). The  $V_T$  shift  $\Delta = \langle V_{\rm T} \rangle$ -V<sub>T<sub>ideal</sub></sub> due to LER is also included for comparison. As expected, the variability increases when the CL or the RMS amplitude of the LER are increased [26]. For both gate length devices,  $\sigma V_T$  is approximately linearly proportional to the RMS height and can reach up to 11.1 mV in the 22 nm gate length NW FET (CL=20 nm and RMS=0.85 nm) and 2.9 times larger value (32.0 mV) in the 10 nm gate length device. The  $V_T$  shift increases with the RMS height and increases also for the smaller CL of 10 nm, a behaviour also observed in FinFETs [20].

The results of this statistical analysis are valuable but they do not provide any spatial information about the effect of the LER on the device performance. Therefore, the feedback provided to semiconductor industry and academia is very limited, without much information regarding how to make improvements in device design. For this reason, we have developed the FSM, that represents the spatial sensitivity of the device under the studied variability source (LER in this case). This allows us to understand how variations happening

in different locations of the device impact the key FoM that characterize the behaviour of the device, hence getting more valuable information that can be used to improve device architecture.

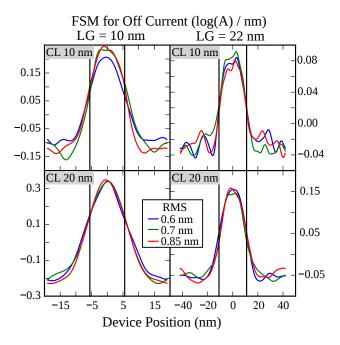

Figure 5.  $I_{\rm off}$  Fluctuation Sensitivity Maps for an off-current along the transport direction in the 10 and 22 nm gate length Si GAA NW FETs at a low drain bias of 0.05 V. The maps are shown for CLs of 10 nm (top) and 20 nm (bottom) and the indicated RMS heights. The maps are obtained from 300 simulations. The area enclosed between the black lines is the gate region.

Fig. 5 shows the  $I_{\rm off}$  FSMs for the the 22 and 10 nm gate length GAA NW FETs due to LER variability generated via realistic profiles. Three different RMS values for 10 nm CL (top figures) and 20 nm CL (bottom figures) were considered. Note that positive/negative FSM values indicate that an increase in the device cross-section will lead to an increase/reduction in the  $I_{\rm off}$  and a zero FSM indicates that there is no change.

For both gate length devices, the gate is the most sensitive region to LER variations, observing the  $I_{\text{off}}$  FSM maximum value at the middle of the device (X=0). A LER induced deformation which makes a device width wider at the source/drain leads to a narrower cross-section in the gate area, and vice versa, as a result of correlations in the LER profiles. The influence of the gate region on the sensitivity of the source/drain is more pronounced when the correlation length is larger, or the device shorter, as seen in Figs. 5 and 6. On the other hand, when the correlation length gets shorter, or the device larger, this effect is reduced and noise appears in the source-drain regions. This can be seen in Figs. 5 and 6 at the top-right subfigures, which are the cases of a lower CL and a larger LG. A similar behaviour was found when studying the metal gate granularity [16], where the device sensitivity was better represented when the grain sizes were large. In the following section we have developed a technique based on synthetic LER profiles that are able to capture the local effect

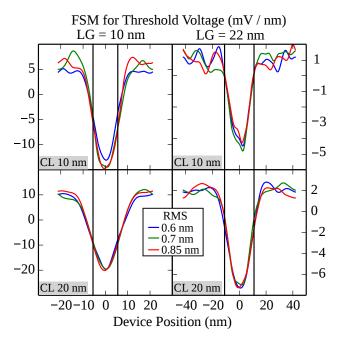

Figure 6.  $V_T$  Fluctuation Sensitivity Maps for a threshold voltage along the transport direction in the 10 and 22 nm gate length Si GAA NW FETs at a low drain bias of 0.05 V. The Maps are constructed for CLs of 10 nm (top) and 20 nm (bottom) and the indicated RMS heights.

of the perturbation, without any non-local interaction.

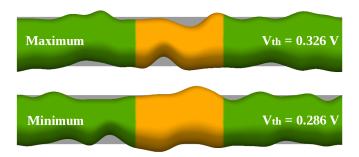

Fig. 6 presents the  $V_T$  FSMs for the the 22 and 10 nm gate length GAA NW FETs due to LER variability generated via realistic profiles. We have found a similar behaviour to the one shown in Fig. 5 but the results have the opposite sign. The sensitivity is lower and positive in the S/D regions, and larger and negative inside the gate area. Therefore, a widening of the device body in the gate region due to LER will imply both a reduction of  $V_T$  and an increase in  $I_{\text{off}}$ . To further demonstrate the validity of this affirmation, Fig. 7 presents schemes of the two GAA NW FETs under LER that produce extreme  $V_T$  values from the statistical distribution shown in Fig. 4 (when CL=10 nm and RMS=0.85 nm). The device that presents a substantial narrowing in the gate region when compared to the non-deformed device (shown in the grey rectangular shadow) requires the largest gate voltage to reach the threshold (top figure of Fig. 7). However, the device that requires the minimum gate voltage to reach the threshold (bottom figure of Fig. 7), has a wider gate than that of the nondeformed device (shown again the grey rectangular shadow).

# B. FSM generated using synthetic LER profiles

As we have mentioned in the previous section, a problem that arises when studying the sensitivity to LER using realistic profiles, generated by Fourier synthesis method, is the spurious contribution of the S/D regions to the FSM. Therefore, in order to isolate the sensitivity of the gate, we have created a large set of synthetic profiles that will apply a single Gaussian vertical deformation at points along the device. This Gaussian deformation has an amplitude of 2 nm, and a full width at half maximum (FWHM) of 1.5 nm. Note that, the actual shape

Figure 7. Maximum and minimum  $V_T$  values induced by the LER variability under 10 nm CL and 0.85 nm RMS deformations in the 22 nm GAA NW FET. The original shape of the device is shown in grey, underneath the figures. Note the device with the maximum  $V_T$  has a smaller width in the gate contact area as predicted in Fig. 6.

Figure 8. Example of the 22 nm gate length Si GAA NW FET affected by synthetic LER profiles that artificially change, only in a small region, the width of the device (top figure) or perform a transversal deviation, creating an offset (bottom figure).

of the perturbation has to be smooth, so it does not have a negative impact in the quality of the underlying mesh when applying the deformation to the device. We have selected the amplitude to represent a similar deformation to a realistic LER, and the FWHM to be as small as possible without impacting the quality of the mesh. Using these synthetic patches, we are able to sweep all the possible locations along the device measuring the spatial sensitivity to LER variations. We have tested two possible synthetic LER scenarios: i) width type deformations, where the centre of the NW does not change but the width of the device at a certain point does (see Fig. 8 top) or ii) offset type deformations, that have a fixed NW width but a varying centre, creating a transversal deviation (offset) at a certain point of the device (see Fig. 8 bottom).

Using the synthetic profiles to understand the sensitivity of the device under deformations will allow us to pinpoint the key locations of the gate that contribute the most to the sensitivity of the device under LER variability. We have localised five regions of the device that are found to be of interest when analysing  $V_T$  and  $I_{\rm off}$ : i) the source region (S), ii) the section of the gate that is near the source–gate border (SG), iii) the middle of the gate (MG), iv) the section of the gate that is near the gate–drain border (GD) and v) the drain region (D).

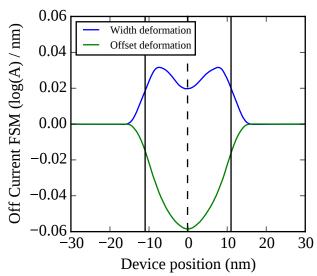

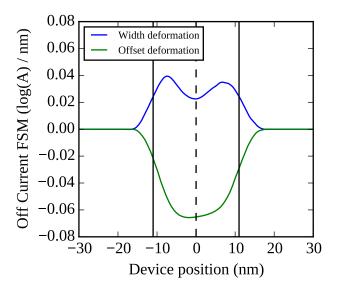

The FSM obtained for the  $I_{\rm off}$  using this synthetic profiles is shown in Fig. 9, for both types of deformations using 120 simulations for each case. In both cases, the sensitivity outside

Figure 9.  $I_{\rm off}$  FSM obtained from the synthetic LER generated for both width and offset deformation types for the 22 nm gate length Si GAA NW FET at a drain bias of 0.05 V. Each set is composed of 120 simulations.

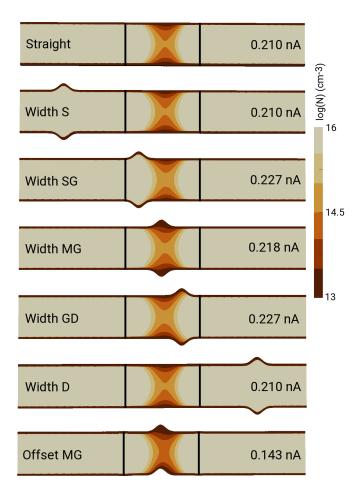

the gate area is close to zero, because the applied deformations are localised and their effect does not extend to other regions of the device. The most sensitive regions of the device to LER variations are located inside the gate area, as also seen before in Fig. 5. When analysing the impact of the gate width deformations on the  $I_{\text{off}}$  FSM, we observe that the sensitivity is positive and has two maxima located in the SG and GD regions, and a minimum located in the middle of the gate. A positive sensitivity indicates that any width type deformation will lead to a overall widening of the device channel and an increase of the  $I_{\rm off}$  when compared to the ideal device with no deformations. In order to understand this behaviour, Fig. 10 presents 2D cross–sectional plots showing the electron concentration (in a logarithmic scale) inside the device at  $V_G$ =0.0 V and  $V_D$ =0.05 V for the five previously indicated key regions and compares them with the ideal device (not affected by any deformation). Note that the iso-surfaces have been adjusted to help visualising the behaviour at the middle of the channel. As expected, both the S and D configurations do not influence the  $I_{\rm off}$  of the device, yielding the same value as the ideal device (the electron concentration inside the device is the same for the Ideal, width S and width D cases). A deformation located inside the gate but near the border of the S/D regions leads to an increase of  $I_{\rm off}$  with respect to the ideal device, which is consistent with both the two maxima observed in the FSM and the increase in the electron concentration seen in the middle of the device (see Fig. 10 width SG and width GD cases). However, if the deformation is placed in the MG,  $I_{\rm off}$  drops with respect to the SG and GD cases due to a decrease in the electron concentration in the middle of the device (see Fig. 10 width MG case). This drop of off-current explains the lower sensitivity seen in the FSM (Fig. 9). We can see in these figures the quantummechanical confinement effect under the gate resulting in the electron concentration being pushed away from the oxidesemiconductor interface [27].

When analysing the impact of the gate offset deformations on the  $I_{\rm off}$  FSM, we observe that the sensitivity inside the gate has a negative sign (opposite behaviour to the width deformations), which means that any offset deformation will lead to a reduction of the  $I_{\rm off}$  with respect to the ideal device (see an example in the bottom cross–section of Fig. 10). Note that the real width of the device channel does not change with an offset deformation, but the effective channel for electrons to flow is reduced, which explains the negative sign of the FSM. The  $I_{\rm off}$  FSM due to offset deformations has only a maximum sensitivity value (with negative sign) located in the MG. The spatial information provided by the FSM can serve as a guide to create LER–resistant device architectures. This information could not be known or understood if only pure statistical analysis (such as the one presented in Fig. 4) is

Fig. 11 shows for the 22 nm gate length Si GAA NW FET, the  $I_{\rm off}$  FSM obtained from the synthetic LER for both width and offset deformation types at a high drain bias of 1.0 V. When analysing the impact of the width deformations in the gate, the two highest sensitivity regions are still located in the SG and GD, but they are not longer symmetric due to the displacement of the potential barrier; placing the maximum sensitivity in the SG, as previously seen in [16] for MGG variations. Similarly, when analysing the impact of the gate offset deformations on the  $I_{\rm off}$  FSM, we observe that the highest sensitivity inside the gate is not longer in the middle of the gate (X=0) but slightly shifted towards the SG region.

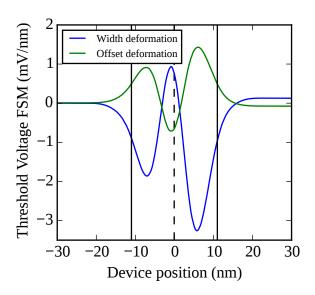

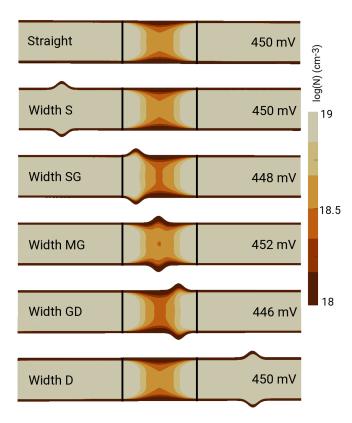

Fig. 12 presents the  $V_T$  FSM calculated from all the configurations of the two synthetic deformation types using 120 simulations per set. As expected, the sensitivity in the S/D region is again close to zero when using the synthetic profiles. Both deformation types affect similarly the  $V_T$  FSM, unlike in the  $I_{\rm off}$  case, although with an opposite sign. The gate region is the most affected by any LER variation. As previously seen with the  $I_{\rm off}$  FSM, the SG, MG and GD regions show distinctive behaviours. Since an offset deformation produces a mirror image of the width one (not in scale) with respect to the  $V_T$  sensitivity, we have limited the analysis to the width type to understand the effect of the placement of a deformation inside the device. Fig. 13 presents 2D cross-sectional plots showing the electron concentration (in a logarithmic scale) inside the device at  $V_G=V_T$  for the five previously indicated key regions and compares them with the ideal device. Here, we have used a constant current criterion of  $(1.47 \ \mu A)$  to determine the  $V_T$  value. A deformation of the width of the device in either the source or drain does not affect the performance of the device. Note that there is no difference between the  $V_T$  of width S and width D cases and that of the ideal device (see Fig. 13), which is consistent with the close-to-zero sensitivity seen in the FSM for the S/D. If the deformation happens in the MG position, there is an increase in  $V_T$  (in agreement with the positive FSM seen in Fig. 12) and in the electron concentration when compared to the ideal device.

In order to understand this increase in electron concentration, we have to bear in mind that following the constant

Figure 10. Illustration of several cross–sections (labels at the left) of the 22 nm gate length GAA NW FET under synthetic LER variability, showing iso–surfaces for the electron concentration (in a logarithmic scale). The cross–section of the straight ideal device is included for comparison at the top. In all cases, the device is polarized at  $V_G=0.0~\rm V$  and  $V_D=0.05~\rm V$  to identify the  $I_{\rm off}$  sensitivity. The corresponding  $I_{\rm off}$  values for each case are also shown (right hand side of the figures).

Figure 11.  $I_{\rm off}$  FSM obtained from the synthetic LER generated for both width and offset deformation types for the 22 nm gate length Si GAA NW FET at a high drain bias of 1.0 V.

current criterion chosen,  $V_T$  is the gate bias at which the current reaches a certain fixed value. Therefore, the MG configuration needs to be more polarised (hence the larger electron concentration) to reach the threshold than the ideal device. A width deformation in either the SG or GD leads to both a reduction in  $V_T$  (consistent with the negative FSM observed in Fig. 12) and in electron concentration in the middle of the gate when compared to the ideal devise. Note that, unlike the  $I_{\rm off}$  FSM where both SG and GD provided the same sensitivity values, the  $V_T$  sensitivity due to LER is larger for the GD region than for the SG (see also their difference in  $V_T$  in Fig. 13). This is due to the influence of a drain bias that becomes more noticeable when a gate voltage is higher.

Figure 12.  $V_T$  Fluctuation Sensitivity Maps for the 22 nm gate length Si GAA NW FET obtained using synthetic profiles that perform either a width or an offset deformation. Each map is obtained from 120 simulations. The drain bias is  $0.05~\rm V$ .

Using the FSM, it is possible to understand where the sensitivity of the device is higher, how several FoM have different sensitivity and also how the behaviour of a transistor changes at a different bias conditions. For instance, the FSM presented in Figs. 9, 11 and 12 are examples of the feedback which this tool is capable to provide to the industry's R&D. Thanks to this tool, the industry can focus its efforts to reduce variability issues in the key locations of a device, or check how new architectures will be affected by these problems.

### IV. PREDICTIVE POWER OF THE FSM

As we mentioned in the previous sections, the FSM represents the sensitivity of the different positions of the device to LER variations, therefore, is expected that it is also capable of obtaining an estimation of the device behaviour under a given LER deformation profile. The first step of this procedure is to obtain the FSM via Equation (1) that we have already done in previous section. Next, these obtained values of FSM can be used to estimate the value of a FoM,  $\phi^k$  affected by a new deformation profile  $d^k$  as follow:

Figure 13. Illustration of several cross–sections of the 22 nm gate length GAA NW FET under synthetic LER variability, showing iso–surfaces for the electron concentration (in a logarithmic scale). The cross–section of the ideal device (top) is included for comparison. The device is polarized at  $V_G = V_T$  (obtained via a constant current criterion) to highlight the  $V_T$  sensitivity.  $V_T$  is shown at the right hand side of each device.

$$\phi^k = \sum_i FSM(x_i)d^k(x_i) \tag{3}$$

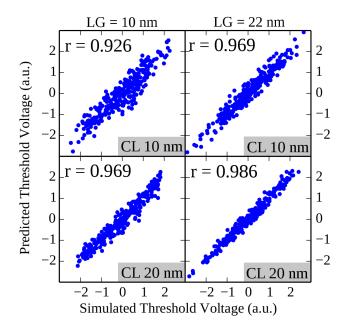

Fig. 14 shows a scatter plot of the simulated  $V_T$  versus the  $V_T$  predicted via the FSM presented in Fig. 6. We have obtained the predicted  $V_T$  values using only the FSM and the deformation profiles, and the values are highly correlated to the originally simulated ones (see correlation coefficient, r, printed inside the figures). We use arbitrary units to show the correlation between the predicted and the simulated values. There is an offset and also a scaling factor between both values, but they have no impact on r. The full procedure to take into consideration the scaling factor and offset was previously shown for MGG variability [16]. Note that, the larger the number of simulations used to calculate the FSM the higher the correlation coefficient will be, because the statistical error will be reduced. This large correlation between the predicted and the fully simulated values confirms that the FSM represents the device sensitivity, and also proves the validity of the FSM as a powerful tool to obtain the spatial dependence of the LER.

Another important benefit of this tool is the ability to provide an accurate prediction of simulation results without having to spend the necessary computational resources to run all the simulations. Using this predictive power capability and in order to save computational time, the FSM can be calculated for a single combination of CL and RMS values, and the other CL and RMS combinations can be estimated with the previous formula, as we have already demonstrated. This method was previously successfully applied [16] to MGG variability.

Figure 14. Scatter plot of the predicted  $V_T$  distribution using the FSM versus the simulated  $V_T$  for the 22 nm (right figures) and 10 nm gate (left figures) length GAA NW FETs as a function of the CL when the RMS height is 0.6 nm. The  $V_T$  values are normalized with respect to the mean value (set at 0). The correlation coefficients (r) are shown to validate the predictive capabilities of the method.

# V. CONCLUSION

A technique based on the creation of a Fluctuation Sensitivity Map (FSM) has been presented for the investigation of LER induced variability in semiconductor transistors. As an example, we have applied the technique to two Si GAA NW FETs with 22 nm and 10 nm gate lengths. The shape and architecture of the 22 nm gate NW FET is modelled from an experimental structure thanks to a FE mesh of the simulation domain. Initially, the LER variability was statistically analysed and presented via histograms. For both gate length devices,  $\sigma V_T$ , increased with both the RMS height and the CL, and reached up to 11.1 mV for the 22 nm gate length device (CL=20 nm and RMS=0.85 nm). The 10 nm NW FET has a value of  $\sigma V_T$  of 32.0 mV, 2.9 times larger than for the 22 nm device. The impact of the  $V_T$  shift due to LER was also studied. We demonstrated that the shift increases with the RMS but decreases with the CL. After that, we used the FSM to investigate the spatial sensitivity of the different regions of the devices under the effect of LER. In order to complete the analysis, we have calculated the sensitivity of the devices using both realistic and synthetic deformation profiles.

We have established pointers using the FSM that could serve as a guidance for the design and fabrication of LERresistant device architectures. We have demonstrated that any LER-type deformation located either in the source or drain regions will not affect the performance of the device. However, if the deformation is located inside the gate, it will significantly affect the device performance. Moreover, the deformation type and its precise location inside the gate plays also an important role. If the deformation widens the channel in the gate region,  $I_{\rm off}/V_T$  will increase/decrease with respect to that of the non–deformed device. If the deformation produces a transversal deviation, the effective channel region will be reduced and  $I_{\rm off}/V_T$  will decrease/increase when compared to that of the straight device. Also, if the deformation widens the channel in the middle of the gate there will be an increase in threshold voltage. If it is located close to the source or to the drain border, the threshold voltage will decrease when compared to that of the straight, LER unaffected NW.

We have also shown the predictive capabilities of the FSM with regard to the  $V_T$ , allowing to obtain the value of the FoM without requiring to run a full set of simulations. The FSM is capable of predicting the threshold voltage value with at least a correlation of r = 0.926 for the worst case scenario.

### **ACKNOWLEDGEMENTS**

This research was supported in part by the Spanish Government under the projects TIN2013-41129-P and TIN2016-76373-P by Xunta de Galicia, FEDER funds (GRC 2014/008) by the Consellería de Cultura, Educación e Ordenación Universitaria (accreditation 2016-2019, ED431G/08), the European Regional Development Fund (ERDF), and by the Spanish Ministry of Economy and Competitiveness and FEDER funds (TEC2014-59402-JIN).

### REFERENCES

- [1] S. Bangsaruntip, G. M. Cohen, A. Majumdar, Y. Zhang, S. U. Engelmann, N. C. M. Fuller, L. M. Gignac, S. Mittal, J. S. Newbury, M. Guillorn, T. Barwicz, L. Sekaric, M. M. Frank, and J. W. Sleight, "High performance and highly uniform gate-all-around silicon nanowire MOSFETs with wire size dependent scaling," in 2009 IEEE International Electron Devices Meeting (IEDM). IEEE, dec 2009, pp. 1–4. [Online]. Available: http://ieeexplore.ieee.org/document/5424364/

- [2] J. J. Gu, Y. Q. Liu, Y. Q. Wu, R. Colby, R. G. Gordon, and P. D. Ye, "First experimental demonstration of gate-all-around IIIV MOSFETs by top-down approach," in 2011 International Electron Devices Meeting, no. 100. IEEE, dec 2011, pp. 33.2.1–33.2.4. [Online]. Available: http://ieeexplore.ieee.org/lpdocs/epic03/wrapper.htm?arnumber=6131662

- [3] A. Asenov, Y. Wang, B. Cheng, X. Wang, P. Asenov, T. Al-Ameri, and V. P. Georgiev, "Nanowire transistor solutions for 5nm and beyond," in 2016 17th International Symposium on Quality Electronic Design (ISQED), no. 001. IEEE, mar 2016, pp. 269–274. [Online]. Available: http://ieeexplore.ieee.org/document/7479212/

- [4] "The International Technology Roadmap for Semiconductors (ITRS)," 2015, (Accessed September 2017). [Online]. Available: http://www.itrs.net/

- [5] "International Roadmap for Devices and Systems (IRDS)," 2016, (Accessed September 2017). [Online]. Available: https://irds.ieee.org/

- [6] N. Agrawal, Huichu Liu, R. Arghavani, V. Narayanan, and S. Datta, "Impact of Variation in Nanoscale Silicon and Non-Silicon FinFETs and Tunnel FETs on Device and SRAM Performance," *IEEE Transactions on Electron Devices*, vol. 62, no. 6, pp. 1691–1697, jun 2015. [Online]. Available: http://ieeexplore.ieee.org/lpdocs/epic03/wrapper.htm?arnumber=7110210

- [7] P. Oldiges, R. Muralidhar, P. Kulkarni, C.-H. Lin, K. Xiu, D. Guo, M. Bajaj, and N. Sathaye, "Critical analysis of 14nm device options," in 2011 International Conference on Simulation of Semiconductor Processes and Devices. IEEE, sep 2011, pp. 5–8. [Online]. Available: http://ieeexplore.ieee.org/lpdocs/epic03/wrapper.htm?arnumber=6035034

- [8] C.-n. Lai, C.-y. Chen, and Y. Li, "Nanosized-metal-grain-induced characteristic fluctuation in gate-all-around si nanowire metal-oxide-semiconductor devices," in 2015 International Workshop on Computational Electronics (IWCE), no. 4. IEEE, sep 2015, pp. 1–4. [Online]. Available: http://ieeexplore.ieee.org/lpdocs/epic03/wrapper.htm?arnumber=7301971

- [9] T. Yu, R. Wang, R. Huang, J. Chen, J. Zhuge, and Y. Wang, "Investigation of Nanowire Line-Edge Roughness in Gate-All-Around Silicon Nanowire MOSFETs," *IEEE Transactions on Electron Devices*, vol. 57, no. 11, pp. 2864–2871, 2010.

- [10] W.-L. Sung, H.-T. Chang, C.-Y. Chen, P.-J. Chao, and Y. Li, "Statistical device simulation of characteristic fluctuation of 10-nm gate-all-around silicon nanowire MOSFETs induced by various discrete random dopants," in 2016 IEEE 16th International Conference on Nanotechnology (IEEE-NANO), vol. 3, no. d. IEEE, aug 2016, pp. 951– 954. [Online]. Available: http://ieeexplore.ieee.org/document/7751556/

- [11] M. A. Elmessary, D. Nagy, M. Aldegunde, N. Seoane, G. Indalecio, J. Lindberg, W. Dettmer, D. Perić, A. J. García-Loureiro, and K. Kalna, "Scaling/LER study of Si GAA nanowire FET using 3D finite element Monte Carlo simulations," Solid-State Electronics, vol. 128, no. 2017, pp. 17–24, feb 2017. [Online]. Available: http://ieeexplore.ieee.org/document/7440050/ http://linkinghub.elsevier.com/retrieve/pii/S0038110116301836

- [12] H. F. Dadgour and K. Banerjee, "Statistical modeling of metal-gate Work-Function Variability in emerging device technologies and implications for circuit design," in 2008 IEEE/ACM International Conference on Computer-Aided Design. IEEE, nov 2008, pp. 270–277. [Online]. Available: http://ieeexplore.ieee.org/lpdocs/epic03/wrapper.htm?arnumber=4681585

- [13] D. Reid, C. Millar, S. Roy, and A. Asenov, "Understanding LER-Induced MOSFET  $V_T$  Variability Part I: Three-Dimensional Simulation of Large Statistical Samples," *IEEE Transactions on Electron Devices*, vol. 57, no. 11, pp. 2801–2807, 2010.

- [14] A. Wettstein, O. Penzin, E. Lyumkis, and W. Fichtner, "Random dopant fluctuation modelling with the impedance field method," in *International Conference on Simulation of Semiconductor Processes and Devices*, 2003. SISPAD 2003. IEEE, 2003, pp. 91–94. [Online]. Available: http://ieeexplore.ieee.org/lpdocs/epic03/wrapper.htm?arnumber=1233645

- [15] D. Reid, C. Millar, G. Roy, S. Roy, and A. Asenov, "Analysis of Threshold Voltage Distribution due to Random Dopants: A 100 000sample 3-D Simulation Study," *IEEE Transactions on Electron Devices*, vol. 56, no. 10, pp. 2255–2263, 2009.

- [16] G. Indalecio, N. Seoane, K. Kalna, and A. J. Garcia-Loureiro, "Fluctuation Sensitivity Map: A Novel Technique to Characterise and Predict Device Behaviour Under Metal Grain Work-Function Variability Effects," *IEEE Transactions on Electron Devices*, vol. 64, no. 4, pp. 1695–1701, apr 2017. [Online]. Available: http://ieeexplore.ieee.org/document/7870589/

- [17] S. Bangsaruntip, K. Balakrishnan, S.-L. Cheng, J. Chang, M. Brink, I. Lauer, R. L. Bruce, S. U. Engelmann, A. Pyzyna, G. M. Cohen, L. M. Gignac, C. M. Breslin, J. S. Newbury, D. P. Klaus, A. Majumdar, J. W. Sleight, and M. A. Guillorn, "Density scaling with gate-all-around silicon nanowire MOSFETs for the 10 nm node and beyond," in 2013 IEEE International Electron Devices Meeting. IEEE, dec 2013, pp. 20.2.1–20.2.4. [Online]. Available: http://ieeexplore.ieee.org/document/6724667/

- [18] A. J. Garcia-Loureiro, N. Seoane, M. Aldegunde, R. Valin, A. Asenov, A. Martinez, and K. Kalna, "Implementation of the Density Gradient Quantum Corrections for 3-D Simulations of Multigate Nanoscaled Transistors," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 30, no. 6, pp. 841–851, jun 2011. [Online]. Available: http://ieeexplore.ieee.org/plb/abs\_all.jsp?arnumber=5768129 http://ieeexplore.ieee.org/ppdocs/epic03/wrapper.htm?arnumber=5768129

- [19] G. Indalecio, M. Aldegunde, N. Seoane, K. Kalna, and A. J. Garcia-Loureiro, "Statistical study of the influence of LER and MGG in SOI MOSFET," Semiconductor Science and Technology, vol. 29, no. 4, p. 045005, apr 2014. [Online]. Available: http://stacks.iop.org/0268-1242/29/i=4/a=045005?key=crossref.978456d880f4570bb66e3e131a28519f

- [20] N. Seoane, G. Indalecio, E. Comesana, M. Aldegunde, A. J. Garcia-Loureiro, and K. Kalna, "Random Dopant, Line-Edge Roughness, and Gate Workfunction Variability in a Nano InGaAs FinFET," *IEEE Transactions on Electron Devices*, vol. 61, no. 2, pp. 466–472, feb 2014. [Online]. Available: http://ieeexplore.ieee.org/lpdocs/epic03/wrapper.htm?arnumber=6691941

- [21] Silvaco, ATLAS User's Manual, Santa Clara, CA, USA, 2012.

- [22] D. M. Caughey and R. E. Thomas, "Carrier Mobilities in Silicon Empirically Related to Doping and Field," in *Proceedings of the IEEE*, vol. 55, no. 12. IEEE, dec 1967, pp. 2192–2193. [Online]. Available: http://ieeexplore.ieee.org/document/1448053/

- [23] K. Yamaguchi, "Field-dependent mobility model for two-dimensional numerical analysis of MOSFET's," *IEEE Transactions on Electron Devices*, vol. 26, no. 7, pp. 1068–1074, july 1979. [Online]. Available: http://ieeexplore.ieee.org/document/1480125/

- [24] N. Seoane, G. Indalecio, E. Comesana, A. J. Garcia-Loureiro, M. Aldegunde, and K. Kalna, "Three-dimensional simulations of random dopant and metal-gate workfunction variability in an In0.53 Ga 0.47 As GAA MOSFET," *IEEE Electron Device Letters*, vol. 34, no. 2, 2013.

- [25] A. Asenov, S. Kaya, and A. Brown, "Intrinsic Parameter Fluctuations in Decananometer MOSFETs Introduced by Gate Line Edge Roughness," *IEEE Transactions on Electron Devices*, vol. 50, no. 5, pp. 1254–1260, may 2003. [Online]. Available: http://ieeexplore.ieee.org/lpdocs/epic03/wrapper.htm?arnumber=1210771

- [26] X. Jiang, X. Wang, R. Wang, B. Cheng, A. Asenov, and R. Huang, "Predictive compact modeling of random variations in FinFET technology for 16/14nm node and beyond," in 2015 IEEE International Electron Devices Meeting (IEDM). IEEE, dec 2015, pp. 727–730. [Online]. Available: http://ieeexplore.ieee.org/document/7409787/

- [27] N. Seoane, G. Indalecio, D. Nagy, K. Kalna, and A. J. Garcia-Loureiro, "Impact of Cross-Sectional Shape on 10-nm Gate Length InGaAs FinFET Performance and Variability," *IEEE Transactions on Electron Devices*, vol. 65, no. 2, pp. 456–462, 2018. [Online]. Available: http://ieeexplore.ieee.org/abstract/document/8246718/