### **Swansea University E-Theses**

# Investigation of wafer processing technologies for the production of low-cost, improved efficiency Si PV cells.

Blayney, Gareth John

How to cite:

Blayney, Gareth John (2014) Investigation of wafer processing technologies for the production of low-cost, improved efficiency Si PV cells.. thesis, Swansea University. http://cronfa.swan.ac.uk/Record/cronfa42531

#### Use policy:

This item is brought to you by Swansea University. Any person downloading material is agreeing to abide by the terms of the repository licence: copies of full text items may be used or reproduced in any format or medium, without prior permission for personal research or study, educational or non-commercial purposes only. The copyright for any work remains with the original author unless otherwise specified. The full-text must not be sold in any format or medium without the formal permission of the copyright holder. Permission for multiple reproductions should be obtained from the original author.

Authors are personally responsible for adhering to copyright and publisher restrictions when uploading content to the repository.

Please link to the metadata record in the Swansea University repository, Cronfa (link given in the citation reference above.)

http://www.swansea.ac.uk/library/researchsupport/ris-support/

Investigation of wafer processing technologies for the production of low-cost, improved efficiency Si PV cells

# **Gareth John Blayney**

A thesis submitted to Swansea University in fulfilment of the requirements for the degree of Doctor of Philosophy

College of Engineering

2014

ProQuest Number: 10805280

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 10805280

Published by ProQuest LLC (2018). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

> ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

#### Abstract

Over the last five years, a dramatic expansion of renewable energy from Photovoltaic (PV) solar cells has been witnessed. This expansion is due in part to wafer based silicon solar cells. Crystalline silicon solar cells currently dominate the PV market because of their low cost per watt of electricity production. In order for silicon solar cells to continue to govern the market, efficiency improvements and cost reductions must be made.

This work focuses on both cost reduction and efficiency improvements, for wafer based silicon solar cells. The main aim of the work was to produce a thin monocrystalline wafer based silicon solar cell. A large proportion of the cost of conventional monocrystalline solar cells is related to the use of high purity silicon substrates. By producing a cell that uses less silicon, significant cost savings can be made. Conventional wafering techniques used in industry are reaching their limit for thin wafer production. The method adopted in this work uses a simple silicon exfoliation technique capable of producing ultrathin silicon foils. A fully operational solar cell was fabricated from a 40µm exfoliated silicon foil. The thin wafer based silicon solar cell was more than four times thinner than a commercially produced equivalent. The work investigated a variety of principles related to the exfoliation and the suitability of the technique for thin photovoltaic devices.

By using a thin exfoliated substrate, conventional anti-reflective (AR) suppressing processes could prove problematic. Experiments were conducted into finding an alternative technique to match the performance of the conventional AR process. The formation of porous silicon (PSi) on the surface of a silicon substrate was found not only to match the commercial process, but to exceed it. With a porous silicon layer, reflectivity was suppressed to just 6.68%. The technique could be applied to both thin silicon solar cells and conventional thicker wafer based cells. The reflectivity suppressive layer could be fabricated in a single simple processing step.

Investigation was also focused upon the top contact for silicon solar cells. As the top of the cell is responsible for current collection and light absorption, large electrical contacts shade the cell resulting in a decrease in efficiency. Silver nanowires (AgNWs) were successfully analysed and deposited onto standard silicon solar cell top contacts as an enhancement coating. Such a coating was found to improve the collection ability of the top contact without causing a significant increase in shading loss. The use of an optimised AgNW coating can increase cell efficiency by as much as 37%.

#### DECLARATION

This work has not previously been accepted in substance for any degree and is not being concurrently submitted in candidature for any degree.

Signed ....

..... (candidate)

Date 04/06/14

#### **STATEMENT 1**

This thesis is the result of my own investigations, except where otherwise stated. Other sources are acknowledged by footnotes giving explicit references. A bibliography is appended.

Signed .....

..... (candidate)

Date 04/06/14

#### **STATEMENT 2**

I hereby give consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside organisations.

Signed .....

..... (candidate)

Date 04/06/14

### Acknowledgements

I would first like to thank my supervisor Dr Owen Guy for giving me the opportunity to work in this exciting research area. His help and guidance along the way has truly been invaluable.

I am also very grateful to have had my work part funded by Purewafer and the European Social Fund (ESF) through the European Union's Convergence programme administered by the Welsh Government. I would like to give a special mention to Simon and Keith at Purewafer, for allowing me to use the facilities at the company and for the inspiring conversations we often had.

I also wish to thank all my past and present colleagues namely Ambroise, Michal, Greg, Ray, Yufei, Steve, Richard, Mark, Sofia, Zari, Connie, Kelly and Celine for their expertise and words of wisdom throughout my project. My thanks also go to the WCPC and SPECIFIC groups, for allowing me to use their specialised equipment.

Of course I owe a huge thank you to my family and friends who have supported me throughout my studies, giving me endless encouragement during the write up.

# Table of Contents

### **Chapter 1: Introduction to Photovoltaics**

| 1.1 | Introduction                           | 1  |

|-----|----------------------------------------|----|

| 1.2 | World Energy Consumption               | 1  |

| 1.3 | Renewable Energy                       | 3  |

| 1.4 | Solar Energy                           | 5  |

| 1.5 | Solar Cell Generations                 | 7  |

| 1.6 | The Future of Photovoltaic Solar Cells | 10 |

| 1.7 | Cost Vs Efficiency                     | 13 |

| 1.8 | Outline of Thesis                      | 16 |

### Chapter 2: Solar Cell Operational Basics

| 2.1 The   | e P-N Junction                                                           | 20 |

|-----------|--------------------------------------------------------------------------|----|

| 2.2 Imp   | portant solar cell parameters                                            | 23 |

|           | 2.2.1 Short Circuit Current (Isc)                                        | 23 |

|           | 2.2.2 Open Circuit Voltage (Voc)                                         | 26 |

|           | 2.2.3 Fill Factor (FF)                                                   | 27 |

| 2.3 Silio | con for Solar Cell Applications                                          | 29 |

|           | 2.3.1 Properties of silicon                                              | 29 |

|           | 2.3.2 Types of Silicon Wafer                                             | 30 |

| 2.4 Wa    | fer Based Silicon Solar Cell Topologies                                  | 32 |

|           | 2.4.1 PERC (Passivated Emitter and Rear Cell)                            | 33 |

|           | 2.4.2 PERL (Passivated Emitter Rear Locally-diffused) silicon solar cell | 34 |

|           | 2.4.3 Back contact solar cells                                           | 35 |

|           | 2.4.4 LGBG (Laser Grooved Buried Grid) Solar Cell                        | 37 |

|           | 2.4.5 HIT Solar Cell                                                     | 38 |

|           |                                                                          |    |

### Chapter 3: Literature Review

| 3.1 Thin Crystalline Silicon |                          | 41 |

|------------------------------|--------------------------|----|

| 3.1.1                        | Layer transfer processes | 42 |

| 3.1.2                        | Etching                  | 44 |

|        | 3.1.3       | Silicon Cleaving                           | 45 |

|--------|-------------|--------------------------------------------|----|

|        | 3.1.4       | Summary                                    | 48 |

| 3.2 S  | olar Cell ( | Optical Loss                               | 49 |

|        | 3.2.1 C     | ptical Losses                              | 49 |

|        |             | 3.2.1.1 Solar Cell Shading                 | 49 |

|        |             | 3.2.1.2 Solar Cell Reflectivity            | 49 |

|        |             | 3.2.1.3 Solar Cell Absorption              | 50 |

|        | 3.2.2 R     | eflectivity Suppression                    | 52 |

|        |             | 3.2.3.1 Anti Reflective Coatings           | 52 |

|        |             | 3.2.3.2 Light Trapping - Surface Texturing | 54 |

|        | 3.2.3 R     | eview of Anti-Reflective Technologies      | 56 |

|        |             | 3.2.3.1 Anti-Reflective Coatings           | 56 |

|        |             | 3.2.3.2 Light Trapping                     | 59 |

|        | 3.2.4 S     | ummary                                     | 62 |

| 3.3 So | lar Cell N  | 1etallisation                              | 64 |

|        | 3.3.1 S     | hunt Resistance                            | 64 |

|        | 3.3.2 S     | eries Resistance                           | 65 |

|        | 3.3.3 C     | onventional Metallisation                  | 68 |

|        | 3.3.4 N     | 1aterials for Metallisation                | 72 |

|        | 3.3.5 F     | ormation of Metallisation                  | 74 |

|        | 3.3.6 P     | rinting Techniques                         | 76 |

|        | 3.3.7 R     | educing Metallisation                      | 78 |

|        | 3.3.8 S     | ummary                                     | 80 |

|        |             |                                            |    |

| Chap   | oter 4: E   | Experimental Methods                       |    |

| 4.1 Fa | abrication  | n Equipment                                | 89 |

|        | 4.1.1 P     | hysical Vapour Deposition                  | 89 |

|        | 4.1.2 C     | hemical Vapour Deposition                  | 89 |

|        | 4.1.3 A     | nnealing Furnaces                          | 90 |

|        | 4.1.4 S     | creen Printing                             | 91 |

| 4.1.4 S         | creen Printing                   | 91 |

|-----------------|----------------------------------|----|

| 4.2 Characteris | ation Equipment                  | 92 |

| 4.2.1           | Solar Simulator/I-V measurements | 92 |

| 4.2.2           | UV-VIS-NIR Spectrophotometer     | 92 |

4.2.3 White Light Interferometry 93

|          | 4.2.4                      | Scanning Electron Microscopy (SEM) with (EDX)                  | 93  |

|----------|----------------------------|----------------------------------------------------------------|-----|

| 4.3 Sola | 4.3 Solar Cell Fabrication |                                                                | 95  |

|          | 4.3.1 St                   | arting Wafer                                                   | 95  |

|          | 4.3.2 W                    | /afer Reclamation                                              | 96  |

|          | 4.3.3 W                    | /afer Grinding/Thinning                                        | 97  |

|          | 4.3.4 S                    | urface Texturing                                               | 97  |

|          | 4.3.5 D                    | oping of n-type emitter junction                               | 98  |

|          | 4.3.6 P                    | hosphorous glass removal, backside grinding and edge isolation | 98  |

|          | 4.3.7 C                    | utting/Dicing                                                  | 99  |

|          | 4.3.8 A                    | RC deposition                                                  | 99  |

|          | 4.3.9 S                    | creen Printing of electrical contacts                          | 100 |

|          | 4.3.10                     | Firing of electrical contacts                                  | 101 |

|          | 4.3.11                     | Cell Testing                                                   | 101 |

# Chapter 5: Ultra-thin Wafer Based Crystalline Silicon

| 5.1 Int | roduction                                                   | 103 |

|---------|-------------------------------------------------------------|-----|

| 5.2 Exp | perimental Procedure                                        | 106 |

| 5.3 Exp | 5.3 Experimentation Results                                 |     |

|         | 5.3.1 Firing Temperature                                    | 107 |

|         | 5.3.2 Contact Thickness                                     | 112 |

|         | 5.3.3 Printing Methods                                      | 115 |

|         | 5.3.4 Exfoliation uniformity in relation to printing method | 116 |

|         | 5.3.5 Substrate Type                                        | 118 |

|         | 5.3.6 Silver Ink Composition                                | 120 |

|         | 5.3.7 Refinement of silicon exfoliation process             | 122 |

|         | 5.3.8 Cell Processing                                       | 124 |

|         | 5.3.8.1 Etching Trials                                      | 124 |

|         | 5.3.8.2 Patterning of Gridlines                             | 125 |

|         | 5.3.8.3 Support structure                                   | 126 |

|         | 5.3.8.4 Efficiency measurements                             | 131 |

| 5.4 Sur | nmary                                                       | 133 |

|         |                                                             |     |

### Chapter 6: Reflectivity Suppression

| 6.1 Introduction                                               | 135 |

|----------------------------------------------------------------|-----|

| 6.2 Experimental Procedure                                     | 136 |

| 6.3 Experimental Results                                       | 137 |

| 6.3.1 Porous Silicon – Metal Assisted Chemical Etching         | 137 |

| 6.3.1.1 Metal Deposition                                       | 137 |

| 6.3.1.2 Chemical Etching                                       | 138 |

| 6.3.1.3 Anti-reflective Properties                             | 140 |

| 6.3.2 Porous Silicon – Substrate Conformal Imprint Lithography | 143 |

| 6.3.3 Porous Silicon – Electrochemical etching                 | 150 |

| 6.3.4 Zinc Oxide nanowires                                     | 153 |

| 6.4 Summary                                                    |     |

# Chapter 7: Silver Nanowire Solar Cell Enhanced Contacts

| 7.1 Introduction                              |     |

|-----------------------------------------------|-----|

| 7.2 Experimental Procedure                    |     |

| 7.3 Experimentation Results                   | 164 |

| 7.3.1 Deposition Trials                       | 164 |

| 7.3.2 Conductivity Trials                     | 170 |

| 7.3.3 Nanowire Conductivity Enhancement       | 173 |

| 7.3.4 Optical Analysis                        | 176 |

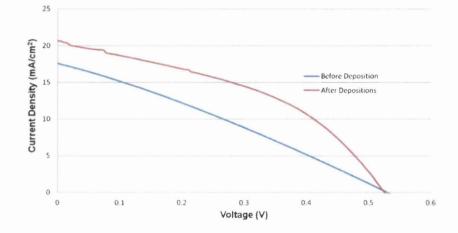

| 7.3.5 Full Textured Silicon Solar Cell Trials | 178 |

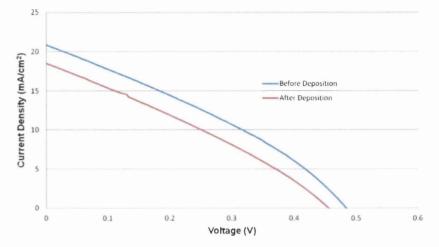

| 7.3.6 Full Polished Silicon Solar Cell Trials | 183 |

| 7.4 Summary                                   | 192 |

|                                               |     |

| Chapter 8: Conclusion                         |     |

|                                               |     |

| Publications                                  | 200 |

| Appendix                                      | 201 |

|                                               |     |

# List of Figures

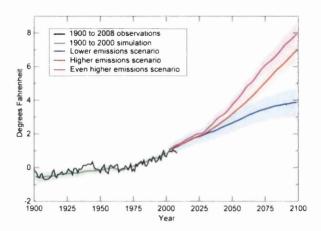

| Figure 1.1: Predicted temperature increase due to emissions                                 | 2  |

|---------------------------------------------------------------------------------------------|----|

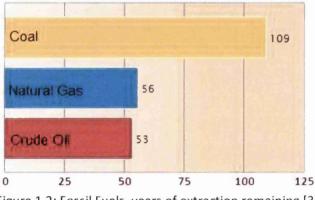

| Figure 1.2: Fossil Fuels, years of extraction remaining                                     | 2  |

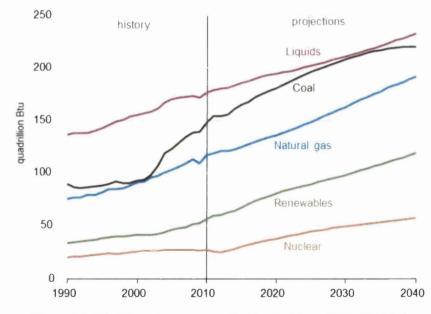

| Figure 1.3: World energy consumption by fuel type 1990-2040                                 | 3  |

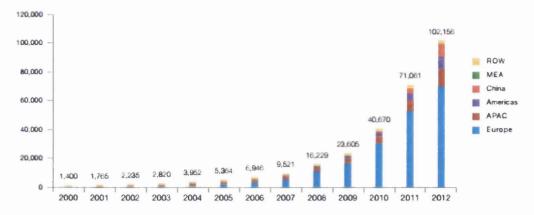

| Figure 1.4: Evolution of global PV cumulative installed capacity 2000-2012                  | 6  |

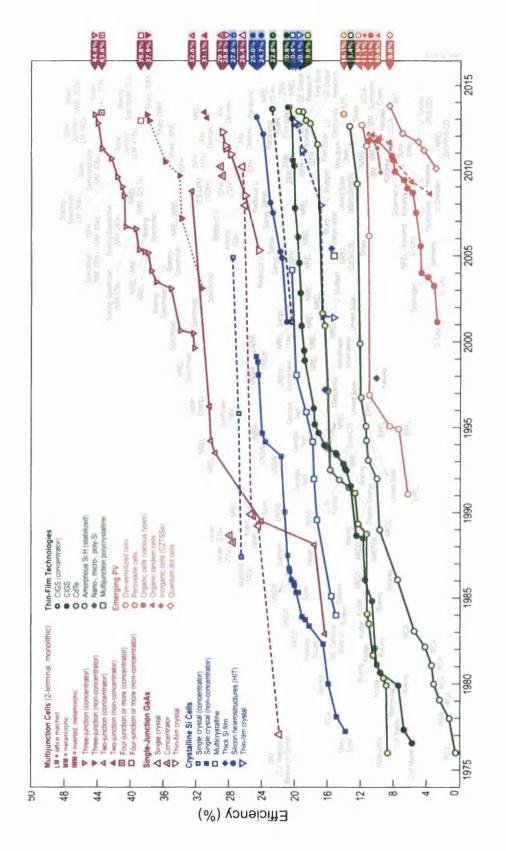

| Figure 1.5: Best research cell efficiencies as of November 2013                             | 9  |

| Figure 1.6: Performance and targets for emerging PV options                                 | 10 |

| Figure 1.7: Chinese manufacturer average panel price                                        | 11 |

| Figure 1.8: Efficiency Cost Profile for different solar generations                         | 13 |

| Figure 1.9: Market share of photovoltaics by each technology type                           | 14 |

| Figure 1.10: Silicon solar cell module cost reductions                                      | 14 |

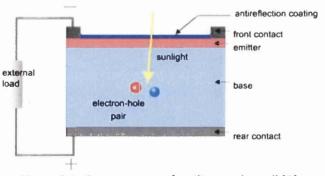

| Figure 2.1: Cross section of a silicon solar cell                                           | 21 |

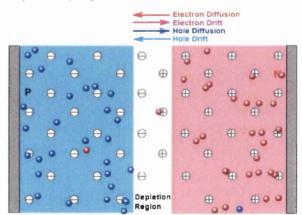

| Figure 2.2: Schematic of a silicon solar cell p-n junction                                  | 22 |

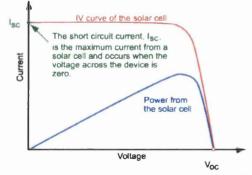

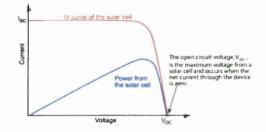

| Figure 2.3: Short circuit current of a solar cell                                           | 23 |

| Figure 2.4: Open circuit voltage of a solar cell                                            | 26 |

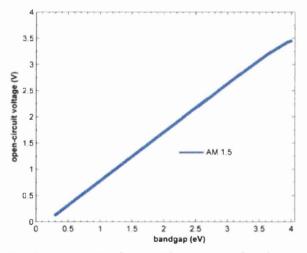

| Figure 2.5: Open circuit voltage with respect to band gap energy                            | 27 |

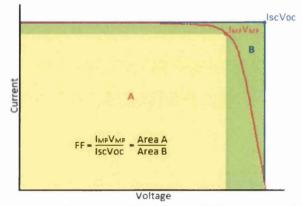

| Figure 2.6: Graphical plot of finding the fill factor of a solar cell                       | 28 |

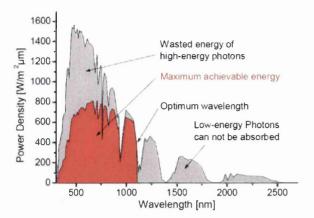

| Figure 2.7: Absorption of a silicon solar cell compared to the solar spectrum               | 30 |

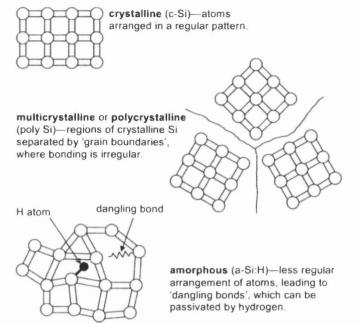

| Figure 2.8: Crystal structure of monocrystalline, multicrystalline and amorphous<br>silicon | 31 |

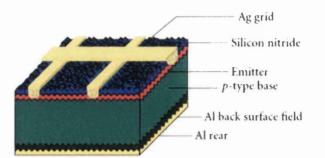

| Figure 2.9: Schematic of a conventional silicon solar cell                                  | 33 |

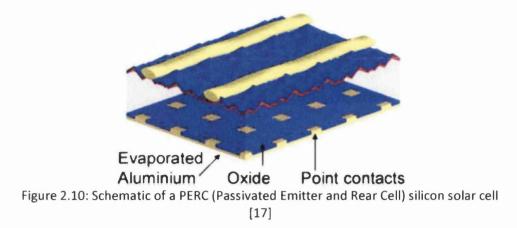

| Figure 2.10: Schematic of a PERC silicon solar cell                                         | 34 |

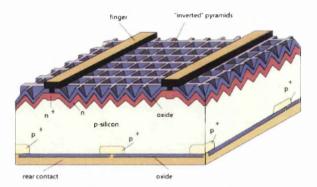

| Figure 2.11: Schematic of a PERL silicon solar cell                                         | 34 |

| Figure 2.12: Schematic of a MWT (Metal-Wrap-Through) Solar Cell                             | 35 |

| Figure 2.13: Schematic of a EWT (Emitter-Wrap-Through) Solar Cell                           | 36 |

| Figure 2.14: Schematic of a BJ (Back Junction) Solar Cell                                   | 37 |

| Figure 2.15: Schematic of a Laser grooved buried grid (LGBG) silicon solar cell             | 37 |

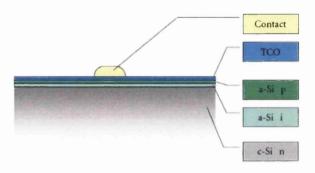

| Figure 2.16: Schematic of a HIT (Heterojunction with Intrinsic Thin layer) Solar Cell       | 38 |

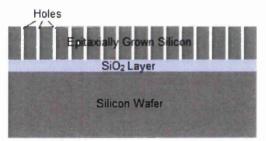

| Figure 3.1: Schematic of VEST structure                                                     | 42 |

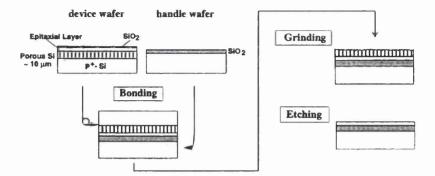

| Figure 3.2: Schematic process flow of ELTRAN                                                | 43 |

| Figure 3.3: Schematic process flow of TIPT                                                  | 43 |

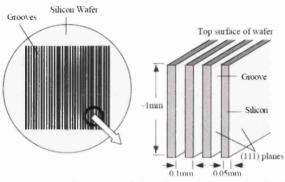

| Figure 3.4: Schematic of the Sliver cell process                                            | 44 |

| Figure 3.5: Schematic of the silicon millefeuille process                                   | 44 |

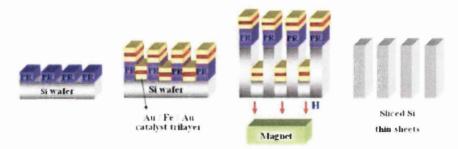

| Figure 3.6: Schematic of the magnetically guided etching process                    | 45  |

|-------------------------------------------------------------------------------------|-----|

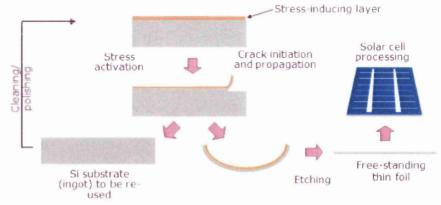

| Figure 3.7: Schematic of the Slim-Cut Process                                       | 47  |

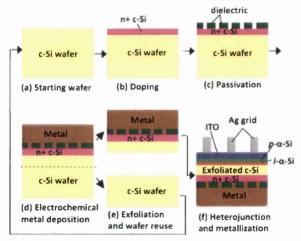

| Figure 3.8: Schematic of the SOM Process                                            | 47  |

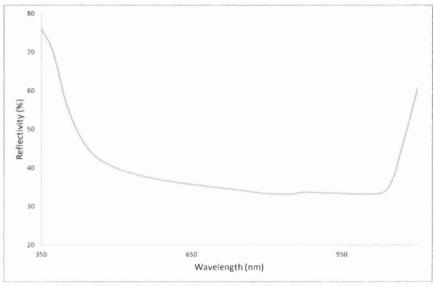

| Figure 3.9: Reflectivity of a polished flat silicon substrate                       | 50  |

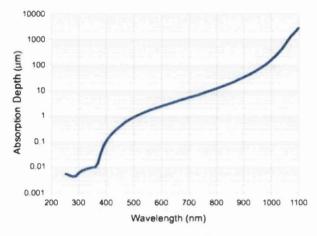

| Figure 3.10: Absorption depth for silicon                                           | 51  |

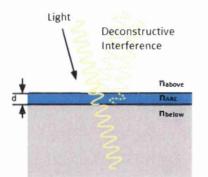

| Figure 3.11: ARC deconstructive interference effects                                | 52  |

| Figure 3.12: Refractive index and related depth of common ARC coatings              | 54  |

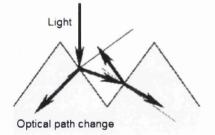

| Figure 3.13: Optical effects of surface texturing                                   | 54  |

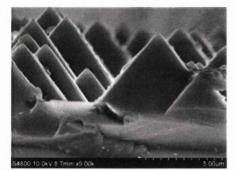

| Figure 3.14: SEM of the surface of textured Si                                      | 55  |

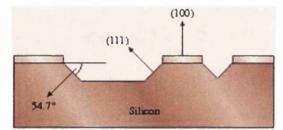

| Figure 3.15: Anisotropic etch profile for (100) silicon wafer                       | 55  |

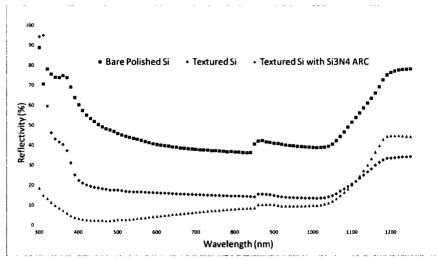

| Figure 3.16: Reflectivity suppression of texturing and ARC techniques               | 56  |

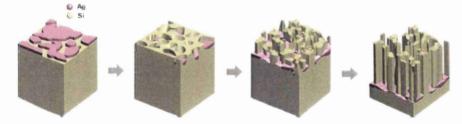

| Figure 3.17: Silver metal assisted etching process                                  | 61  |

| Figure 3.18: Schematic of the main series resistive components                      | 66  |

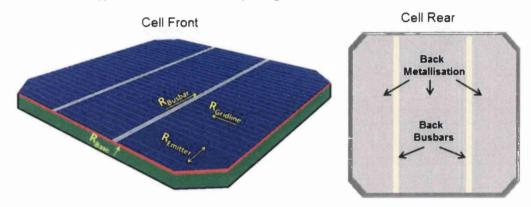

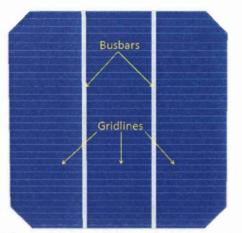

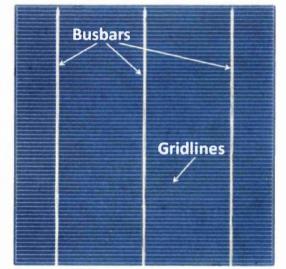

| Figure 3.19: Typical silicon solar cell with two busbar top contact                 | 67  |

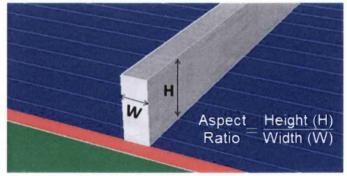

| Figure 3.20: High aspect ratio front contact                                        | 67  |

| Figure 3.21: Solder tabbing wire connection between solar cells                     | 68  |

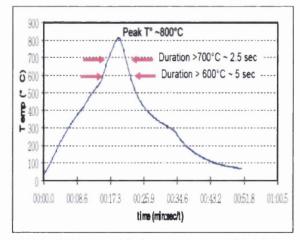

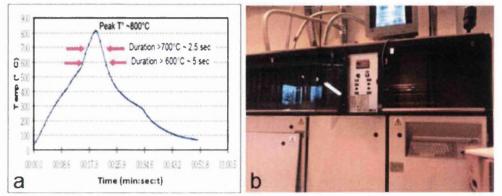

| Figure 3.22: Typical firing profile for screen printable silver paste               | 69  |

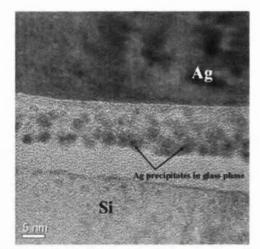

| Figure 3.23: HR TEM Image of contact interface between silicon and silver           | 71  |

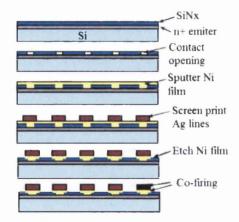

| Figure 3.24: Schematic of a front contact process using a thin nickel layer         | 72  |

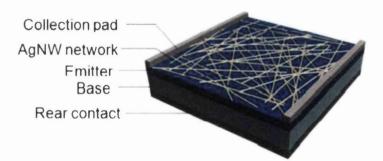

| Figure 3.25: Silver nanowire mesh top contact                                       | 74  |

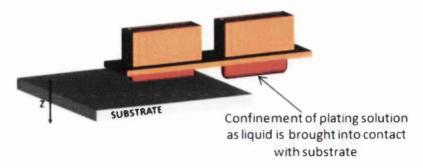

| Figure 3.26: Mechanism of DLM formation as substrate approaches the DLD             | 76  |

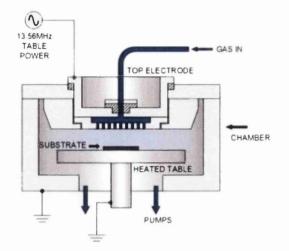

| Figure 4.1: PECVD equipment schematic                                               | 90  |

| Figure 4.2: Schematic of screen printing process                                    | 91  |

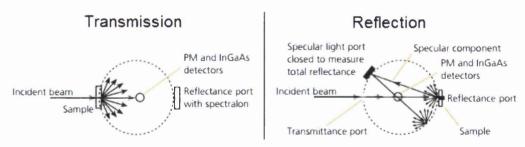

| Figure 4.3: Spectrophotometer schematic of transmission and reflection measurements | 92  |

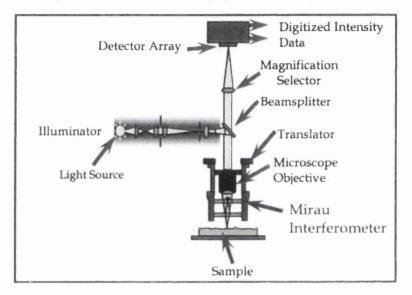

| Figure 4.4: Schematic of white light interferometer setup                           | 93  |

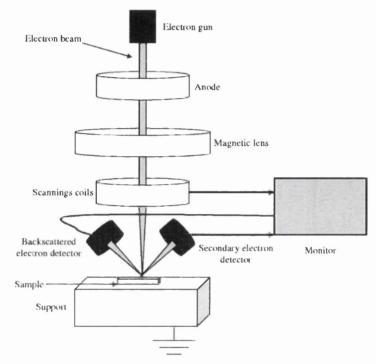

| Figure 4.5: Schematic of scanning electron microscopy equipment                     | 94  |

| Figure 4.6: Mechanical grinding equipment for wafer thinning                        | 97  |

| Figure 4.7: SEM of textured silicon by KOH etching                                  | 98  |

| Figure 4.8: N-type emitter doping using POCI furnace                                | 98  |

| Figure 4.9: Dicing of circular 200mm silicon wafer                                  | 99  |

| Figure 4.10: SiN ARC coating on textured Si substrate                               | 100 |

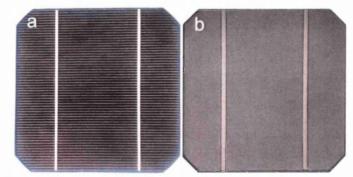

| Figure 4.11: Electrical Contacts a) Front surface b) Rear Surface                   | 100 |

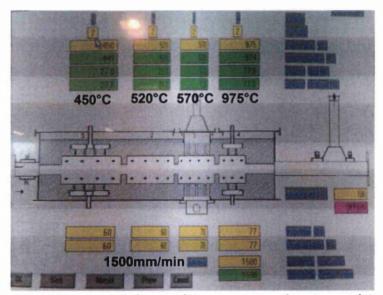

| Figure 4.12: a) Contact firing profile, b) 4 Zone firing furnace                    | 101 |

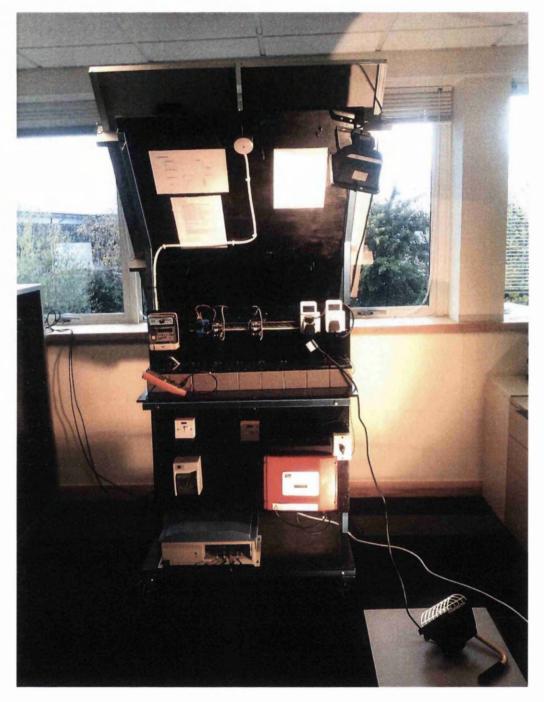

| Figure 4.13: Oriel solar tester equipment used to measure cell performance          | 101 |

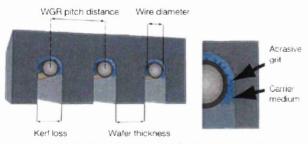

| Figure 5.1: Multi-wire saw wafering schematic                                                                             | 103 |

|---------------------------------------------------------------------------------------------------------------------------|-----|

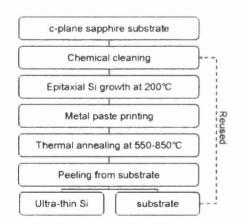

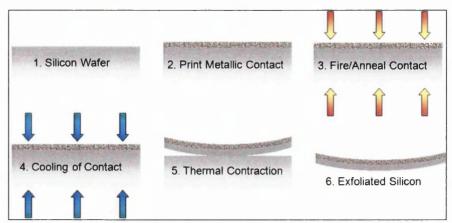

| Figure 5.2: Silicon Exfoliation Process                                                                                   | 105 |

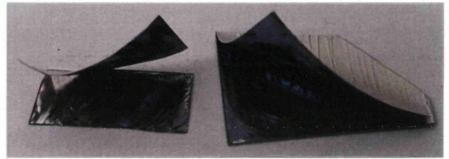

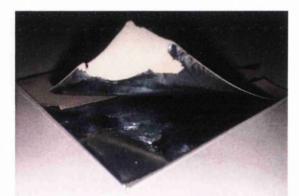

| Figure 5.3: Silicon foil and corresponding metallic layer (after exfoliation)                                             | 105 |

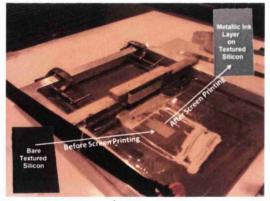

| Figure 5.4: Image of screen printing apparatus                                                                            | 107 |

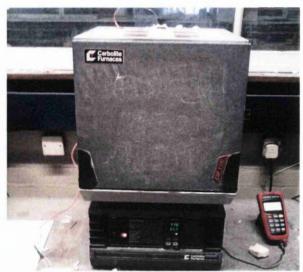

| Figure 5.5: Single zone electric furnace                                                                                  | 108 |

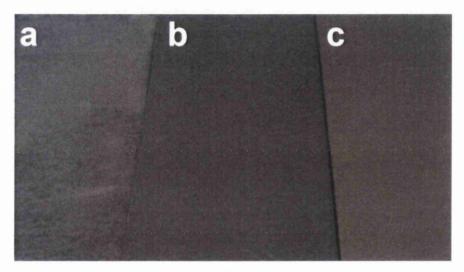

| Figure 5.6: Aluminium contacts after firing (a) Under-fired,<br>(b) Optimally fired, (c) Over-fired                       | 110 |

| Figure 5.7: Sample with two screen printed layers of silver paste, resulting in exfoliation of a small area of the sample | 112 |

| Figure 5.8: Sample with two screen printed layers of: a) aluminium paste, b) aluminium silver paste                       | 113 |

| Figure 5.9: Sample with three screen printed layers of silver paste                                                       | 113 |

| Figure 5.10: Thickness measurement for double screen printed silver contact using white light interferometry              | 114 |

| Figure 5.11: (a) Partially exfoliated stencil contact,<br>(b) Thickness measurement of contact.                           | 115 |

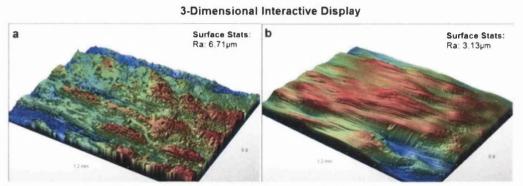

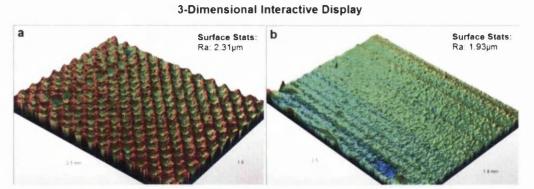

| Figure 5.12: 3D topography of (a) Screen printed foil, (b) Stencil coated foil                                            | 116 |

| Figure 5.13: 3D topography of (a) Screen printed contact,<br>(b) Stencil coated contact                                   | 117 |

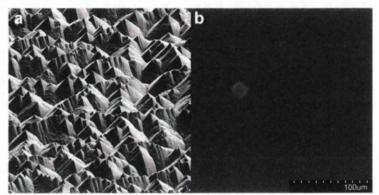

| Figure 5.14: (a) Textured Silicon Surface, (b) Polished Silicon Surface                                                   | 118 |

| Figure 5.15: (a) Polished wafer after firing process,<br>(b) Textured wafer after firing process                          | 118 |

| Figure 5.16: Stencil coated PV17A silver contact on textured silicon after firing                                         | 120 |

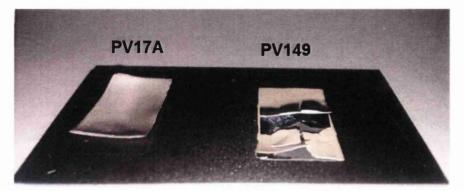

| Figure 5.17: Stencil coated PV17A and PV149 silver contacts on textured silicon substrate after firing                    | 121 |

| Figure 5.18: Four zone belt furnace firing parameters for silicon exfoliation                                             | 122 |

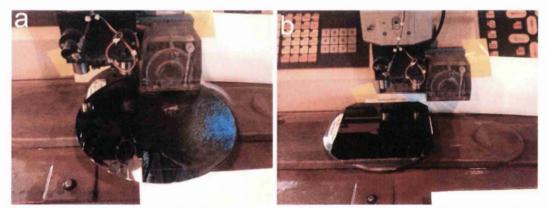

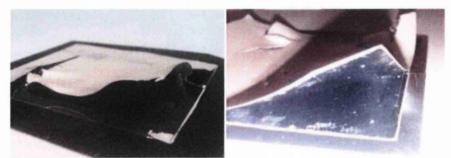

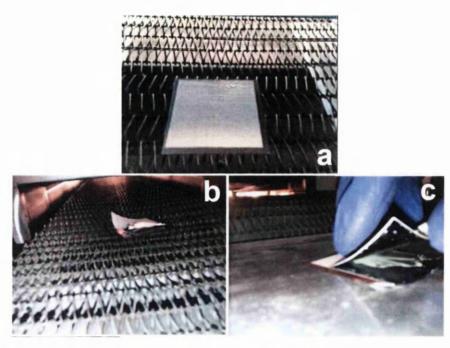

| Figure 5.19: Silver coated sample (a) Entering furnace, (b) Exiting furnace, (c) After firing                             | 123 |

| Figure 5.20: Silver Metallic contact removal in<br>Ammonia/Hydrogen Peroxide/Water etchant                                | 124 |

| Figure 5.21: Textured silicon foil after metallic contact removal                                                         | 125 |

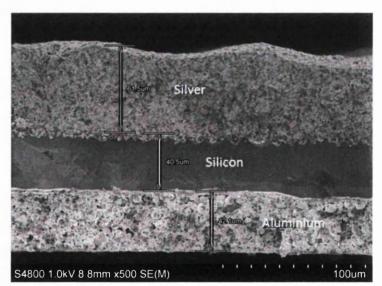

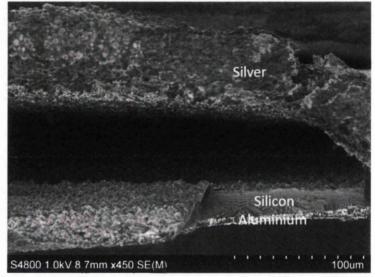

| Figure 5.22: SEM imaging of cross section of exfoliated sample with aluminium rear contact                                | 127 |

| Figure 5.23: Silver contact detachment from silicon foil substrate                                                        | 128 |

| Figure 5.24: SEM image of silicon surface after silver contact removal                                                    | 129 |

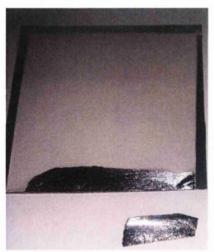

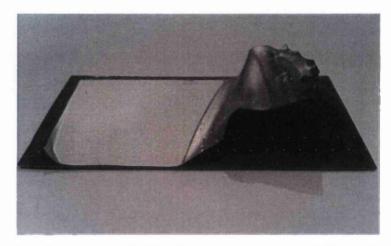

| Figure 5.25: Silicon foil and metallic contact after separation                                                           | 129 |

| Figure 5.26: SEM image of silicon foil after silver front contact removal                                                 | 130 |

| Figure 5.27: Fully processed 40 $\mu$ m thin silicon solar cell with textured surface                                     |     |

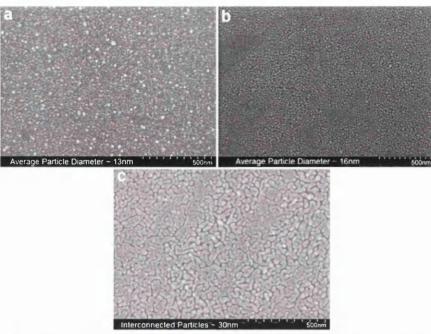

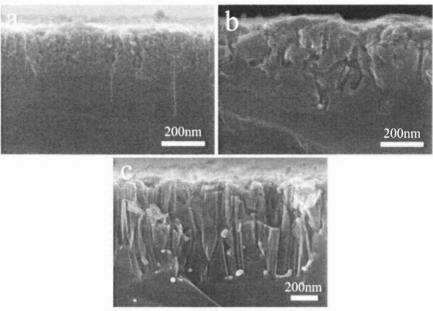

| Figure 6.1: SEM Image of Si with deposition of a) 2nm Ag, b) 5nm Ag<br>and c) 10nm Ag                                  | 138 |

|------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.2: 2nm Ag deposition a) Before etching, b) After 60s etch.                                                    | 138 |

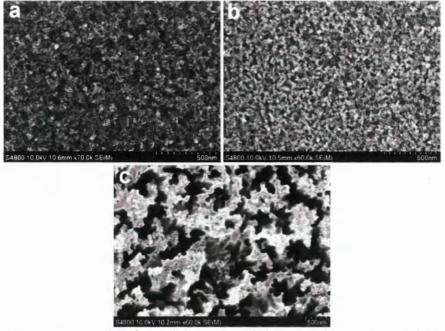

| Figure 6.3: SEM Image of PSi formed deposition of a) 2nm Ag, b) 5nm Ag and c) 10nm Ag from chemical etching in HF/H2O2 | 139 |

| Figure 6.4: Cross-section of PSi from deposition of a) 2nm Ag,<br>b) 5nm Ag and c) 10nm Ag                             | 140 |

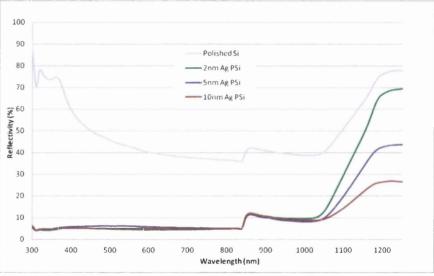

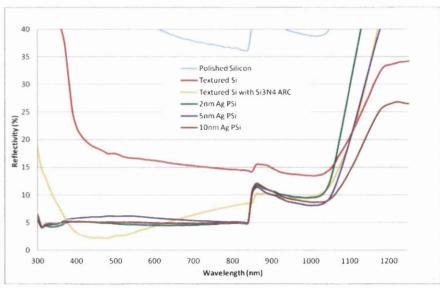

| Figure 6.5: Reflectivity suppression of PSi                                                                            | 141 |

| Figure 6.6: Reflectivity of PSi compared to commercial process                                                         | 142 |

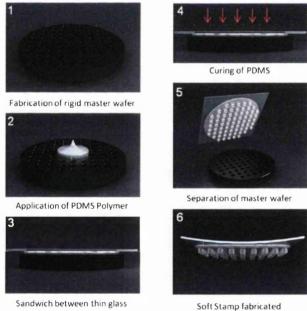

| Figure 6.7: SCIL Stamp Replication Process Schematic.                                                                  | 143 |

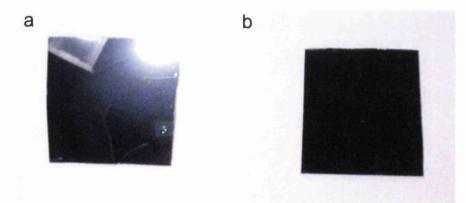

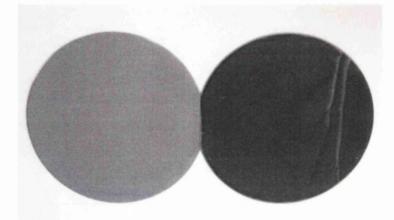

| Figure 6.8: Image of Silicon wafer before and after PSi formation                                                      | 144 |

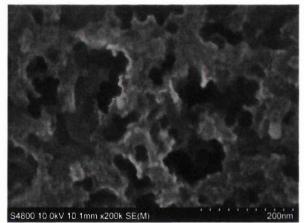

| Figure 6.9: SEM conformation of PSi formation                                                                          | 144 |

| Figure 6.10: Silicon wafer before and after FDTS treatment                                                             | 145 |

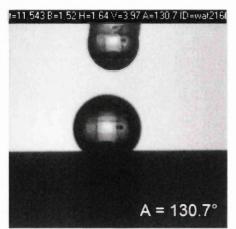

| Figure 6.11: Contact Angle of PSi wafer surface after FDTS layer                                                       | 146 |

| Figure 6.12: SEM of FDTS layer a) Surface, b) Cross section                                                            | 146 |

| Figure 6.13: SCIL Stamp replication of PSi features using master replication tool                                      | 147 |

| Figure 6.14: SCIL Stamp separation tool                                                                                | 147 |

| Figure 6.15: PSi detachment from Si base                                                                               | 148 |

| Figure 6.16: Cavities between PDMS and PSI                                                                             | 149 |

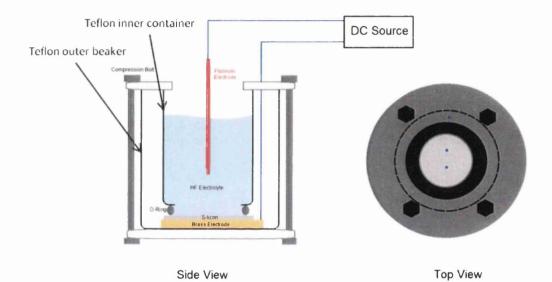

| Figure 6.17: Design of chamber for electrochemical etching of PSi                                                      | 150 |

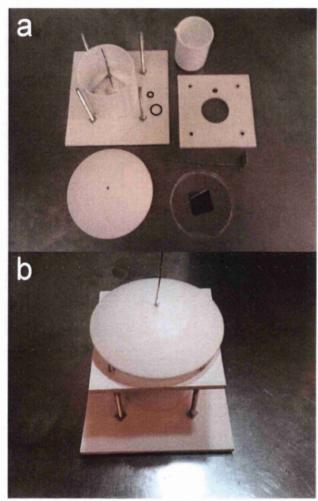

| Figure 6.18: a) Chamber components and b) Fully assembled chamber                                                      | 151 |

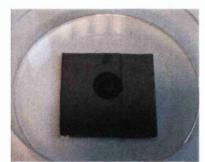

| Figure 6.19: Si substrate after etch at 1.5V, 15.4mA for 2minutes                                                      | 152 |

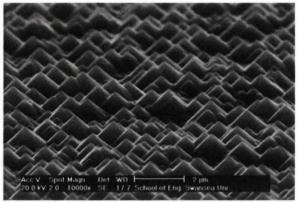

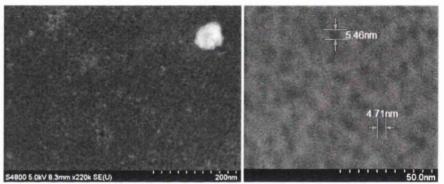

| Figure 6.20: SEM of Si substrate after etch at 1.5V, 15.4mA for 2minutes                                               | 152 |

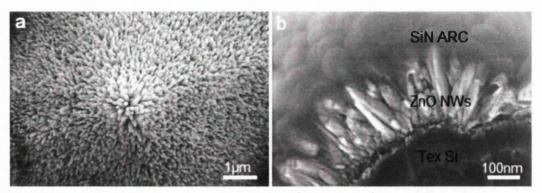

| Figure 6.21: ZnO nanowires on textured Si, a) Top view, b) Cross-sectional view                                        | 154 |

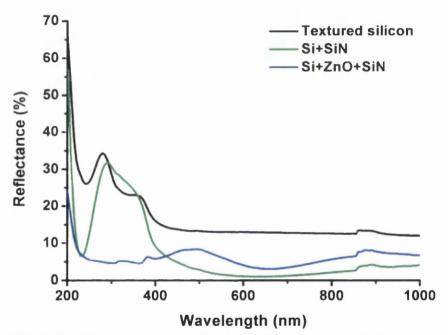

| Figure 6.22: Reflectivity measurement of textured silicon surface with SiN and ZnO+SiN                                 | 154 |

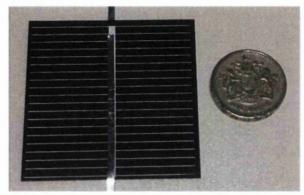

| Figure 6.23: Fully fabricated reclaimed silicon solar cell with the ZnO and SiN combined ARC                           | 155 |

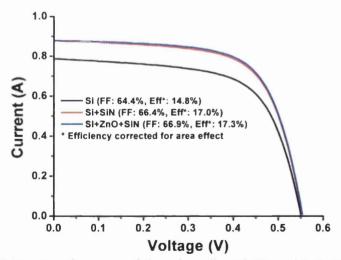

| Figure 6.24: I-V performance of the solar cells with SiN and ZnO+SiN ARC                                               | 155 |

| Figure 7.1: Typical silicon solar cell with three busbar top contact arrangement                                       | 160 |

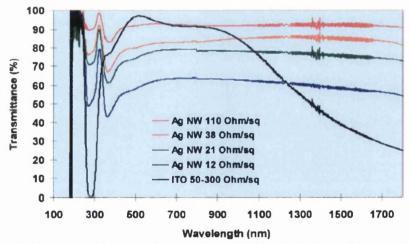

| Figure 7.2: Optical transmittance of transparent Ag NW electrodes                                                      | 161 |

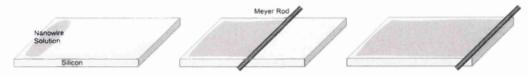

| Figure 7.3: Silver nanowire rod coating procedure                                                                      | 164 |

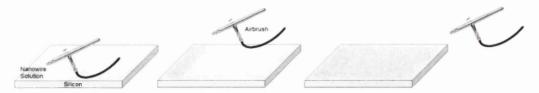

| Figure 7.4: Silver nanowire spray coating procedure                                                                    | 165 |

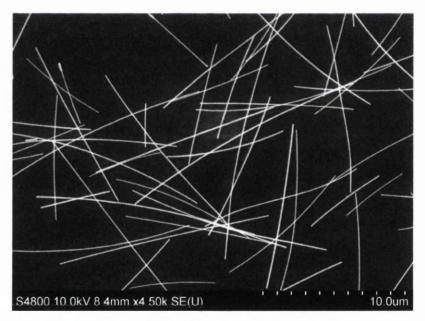

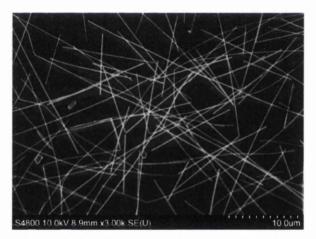

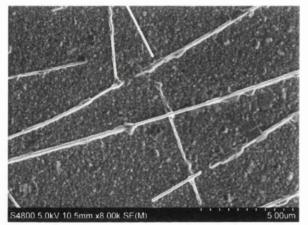

| Figure 7.5: Rod Coated AgNW's on Polished Si Substrate                                                                 | 165 |

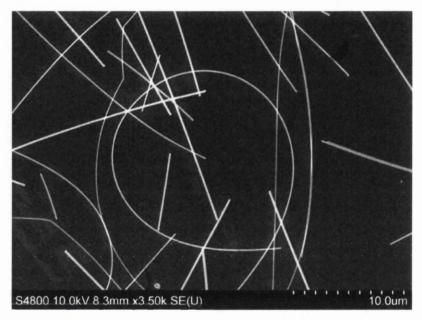

| Figure 7.6: Spray Coated AgNW's on Polished Si Substrate                                                               | 166 |

|                                                                                                                        |     |

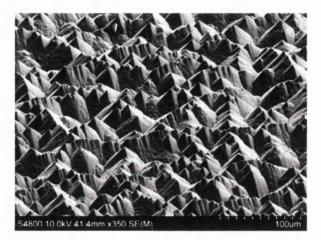

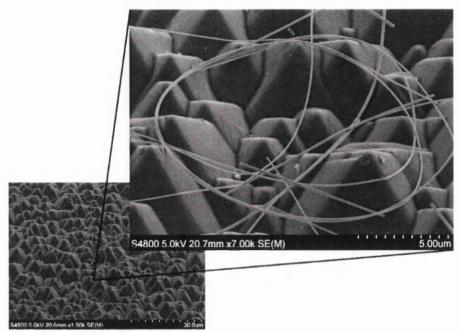

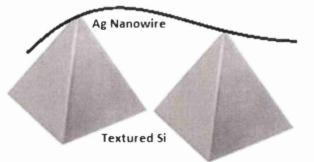

| Figure 7.7: SEM image of pyramidal micro-texted surface of a typical silicon solar cell                                                                                | 167 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

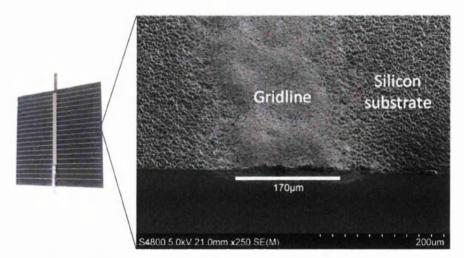

| Figure 7.8: SEM image of a silicon solar cell front contact gridline                                                                                                   | 167 |

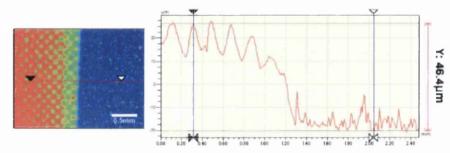

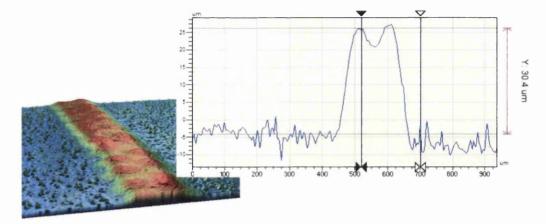

| Figure 7.9: Interferometry (3D and line profile) of front contact gridline step height change relative to the silicon substrate                                        | 168 |

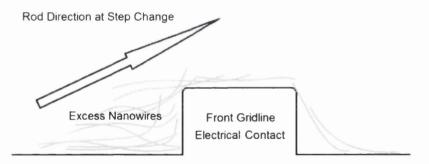

| Figure 7.10: Depiction of step change on rod coating silver nanowires                                                                                                  | 168 |

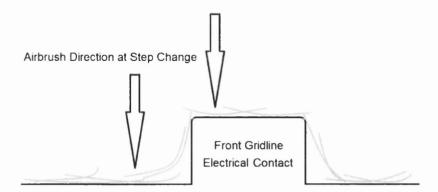

| Figure 7.11: Depiction of step change on spray coating silver nanowires                                                                                                | 169 |

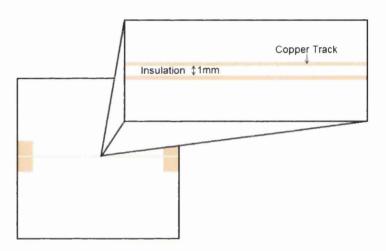

| Figure 7.12: PCB layout of copper tracks on insulating substrate for silver nanowire conductivity trials                                                               | 170 |

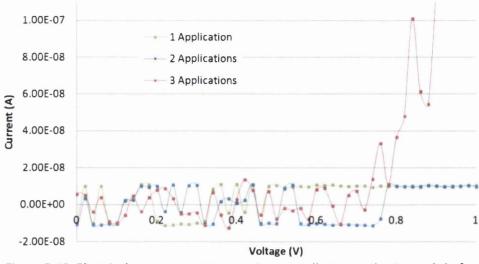

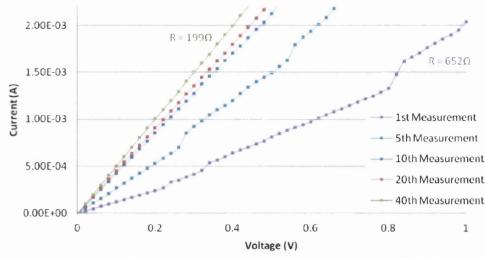

| Figure 7.13: Electrical measurement across 1mm gap<br>(between the Cu tracks) after application of nanowire layers                                                     | 171 |

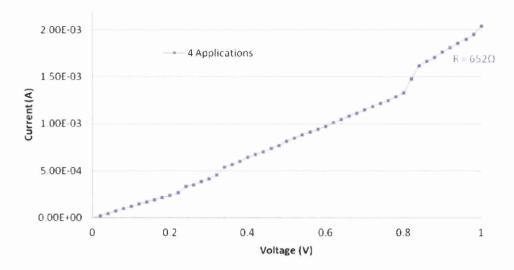

| Figure 7.14: Electrical measurement across 1mm gap after application of 4th nanowire layer                                                                             | 172 |

| Figure 7.15: SEM of 4 layers of silver nanowires                                                                                                                       | 172 |

| Figure 7.16: Silver nanowires annealed at 180°C for 10minutes                                                                                                          | 173 |

| Figure 7.17: Repeated I-V measurements across 1mm gap decreased the electrical resistance of AgNW mesh (after 4 layers)                                                | 174 |

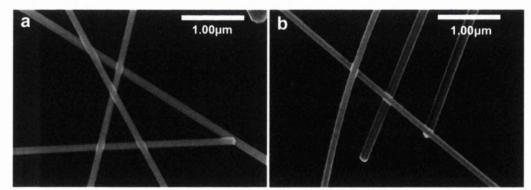

| Figure 7.18: SEM images of nanowire junction: (a) Before electrical measurements (b) After 50 electrical measurements                                                  | 174 |

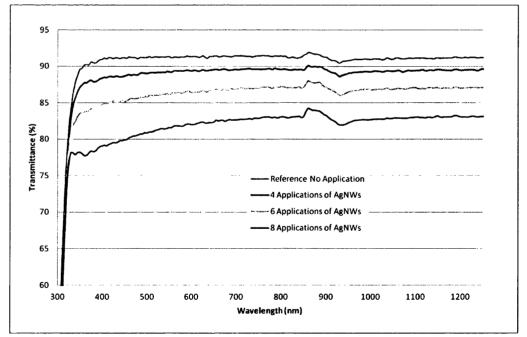

| Figure 7.19: Transmittance of glass substrate after AgNW applications                                                                                                  | 176 |

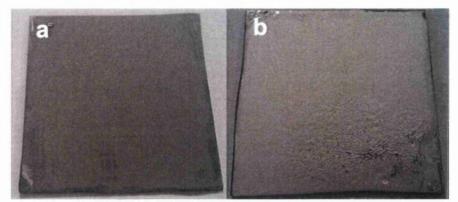

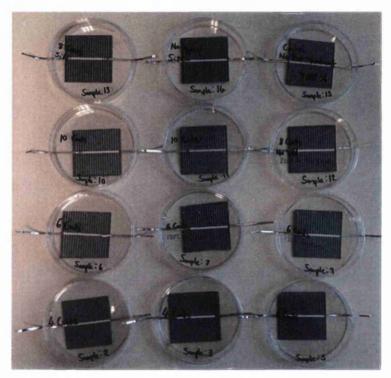

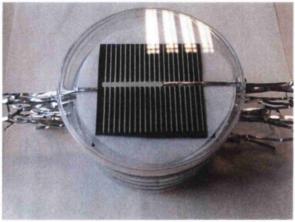

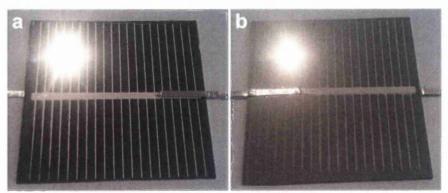

| Figure 7.20: Fabricated textured silicon solar cells                                                                                                                   | 179 |

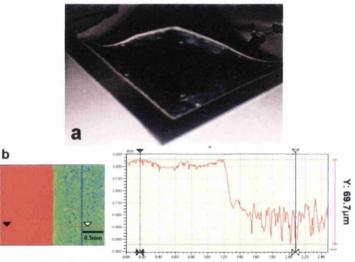

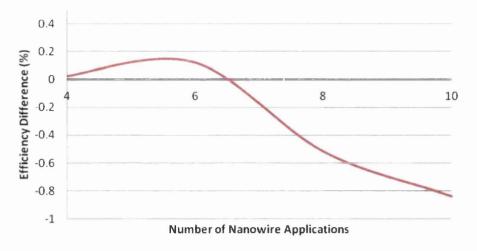

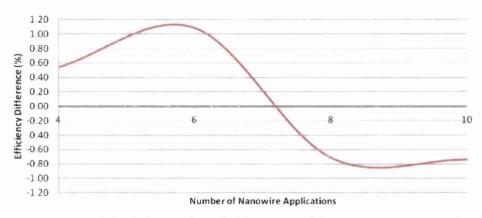

| Figure 7.21: Solar cell efficiencies before and after nanowire depositions                                                                                             | 181 |

| Figure 7.22: Textured silicon solar cell after 6 nanowire applications                                                                                                 | 182 |

| Figure 7.23: Illustration of nanowire contact points between textured silicon pyramids                                                                                 | 182 |

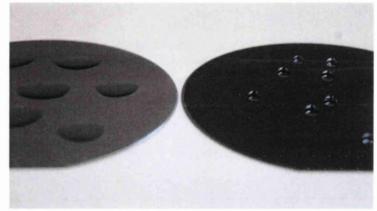

| Figure 7.24: Fabricated polished silicon solar cells                                                                                                                   | 183 |

| Figure 7.25: Polished silicon solar cells with (a) 4 AgNW Applications, (b) 10 AgNW Applications                                                                       | 184 |

| Figure 7.26: Polished silicon solar cell efficiency modification after nanowire depositions                                                                            | 185 |

| Figure 7.27: Silver nanowires on surface of polished silicon solar cell                                                                                                | 188 |

| Figure 7.28: SEM image of polished cells with a) 4 nanowire applications,<br>b) 6 nanowire applications, c) 8 nanowire applications and d) 10 nanowire<br>applications | 189 |

| Figure 7.29: SEM and EDX analysis of irregular polished cell with 6 nanowire applications                                                                              | 190 |

# List of Tables

| Table 1.1: Renewable electricity generation (billion kilowatt-hours) by energy source                 | 5   |

|-------------------------------------------------------------------------------------------------------|-----|

| Table 1.2: 2010 UK solar feed in tariff                                                               | 7   |

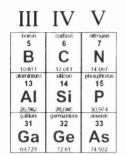

| Table 2.1: Group III to IV of the periodic table                                                      | 21  |

| Table 5.1: Firing temperature in relation to contact adhesion                                         | 109 |

| Table 5.2: Efficiency measurement for $40\mu m$ thick exfoliated silicon solar cell                   | 132 |

| Table 7.1: Silicon Solar Cell Average Efficiencies before nanowire deposition                         | 179 |

| Table 7.2: Applications of nanowire solution received for each sample group                           | 179 |

| Table 7.3: Silicon solar cell average efficiencies before and after nanowire           depositions    | 180 |

| Table 7.4: Silicon Solar Cell Average Efficiencies before nanowire deposition                         | 183 |

| Table 7.5: Applications of nanowire solution received for each sample group                           | 184 |

| Table 7.6: Silicon solar cell average efficiencies before and after nanowire           depositions    | 185 |

| Table 7.7: Electrical efficiency measurement of polished cell with 6 nanowire           applications  | 186 |

| Table 7.8: Electrical efficiency measurement of polished cell with 10           nanowire applications | 188 |

|                                                                                                       |     |

### List of Abbreviations

| A.C.      | Alternating Current                               |

|-----------|---------------------------------------------------|

| AC<br>ARC | Alternating Current                               |

| a-Si      | Anti Reflective Coating                           |

| BJ        | Amorphous Silicon<br>Back Junction                |

| BSF       | Back Surface Field                                |

| Cds       |                                                   |

|           | Cadmium Sulphide                                  |

| CdTe      | Cadmium Telluride                                 |

| CIGS      | Copper Indium Gallium Selenide                    |

| CPV       | Concentrated Photovoltaics                        |

| CTE       | Coefficient of Thermal Expansion                  |

| DC        | Direct Current                                    |

| DLD       | Dynamic Liquid Drop                               |

| DSSC      | Dye-Sensitised Solar Cells                        |

| EBL       | Electron Beam Lithography                         |

| EDX       | Energy-Dispersive X-ray                           |

| ELTRAN    | Epitaxial Layer TRANsfer                          |

| EWT       | Emitter Wrap Through                              |

| FIT       | Feed in Tariff                                    |

| HIT       | Heterojunction with Intrinsic Thin layer          |

| ITO       | Indium Tin Oxide                                  |

| LGBG      | Laser Grooved Buried Grid                         |

| LPCVD     | Low Pressures Chemical Vapour Deposition          |

| MAE       | Metal Assisted Etching                            |

| MWT       | Metal Wrap Through                                |

| NIL       | Nanoimprint Lithography                           |

| OPV       | Organic Photovoltaics                             |

| PCB       | Printed Circuit Board                             |

| PECVD     | Plasma Enhanced Chemical Vapour Deposition        |

| PERC      | Passivated Emitter and Rear Cell                  |

| PERL      | Passivated Emitter Rear Locally-diffused          |

| PESC      | Passivated Emitter Solar Cell                     |

| PSi       | Porous Silicon                                    |

| PV        | Photovoltaic                                      |

| PVD       | Physical Vapour Deposition                        |

| SCIL      | Substrate Conformal Imprint Lithography           |

| SEM       | Scanning Electron Microscopy                      |

| SLIM      | Stress induced Liftoff Method                     |

| SOM       | Silicon On Metal                                  |

| SRH       | Shockley-Read-Hall                                |

| TCE       | Transparent Conducting Electrodes                 |

| TF        | Thin Film                                         |

| τιρτ      | Thermal-stress Induced Pattern Transfer           |

| VEST      | Via hole Etching for the Separation of Thin films |

|           |                                                   |

# List of Symbols

| FF              | Fill Factor                           |

|-----------------|---------------------------------------|

| G               | Generation rate                       |

| I <sub>MP</sub> | Current at the measured maximum power |

| l <sub>sc</sub> | Short Circuit Current                 |

| L <sub>n</sub>  | Electron diffusion length             |

| Lp              | Hole diffusion length                 |

| ή               | Efficiency                            |

| V <sub>MP</sub> | Voltage at the measured maximum power |

| V <sub>oc</sub> | Open Circuit Voltage                  |

| ΙL              | Light generated current               |

| I <sub>o</sub>  | Saturation current                    |

| Jι              | Light generated current density       |

| Jo              | Saturation current density            |

| Pin             | Power input                           |

| Pmax            | Maximum power                         |

| n               | Refractive index                      |

| $n_{ m ARC}$    | Refractive index of the ARC layer     |

| q               | Absolute value of electron charge     |

### **Chapter 1: Introduction to Photovoltaics**

#### **1.1 Introduction**

This chapter discusses the essential need for renewable energy sources in order to start replacing conventional fossil fuelled and nuclear power stations. Renewable energy technologies will be briefly reviewed and advantages given for the use of photovoltaic (PV) solar cells. In particular the different generations of solar cell technology will also be reviewed in relation to their corresponding efficiencies. A brief overview of the PV market has also been included. Silicon solar cells will be shown to dominate this market and the reasons for such domination are discussed. PV research is closely related to market trends and as well as improved efficiency, cost and manufacturing issues must be considered as part of any research and development strategy. Finally, the aim of the research in this work will be outlined along with justifications of the importance of the experimental study.

#### **1.2 World Energy Consumption**

Since the widespread use of electricity, mankind's dependence upon it has grown exponentially. In 2010, the world produced over 20.2 trillion kilowatt-hours of electricity, and this figure is predicted to grow to 39.0 trillion kilowatt-hours by 2040 [1]. Electrical consumption is almost certainly set to rise year on year, but the methods by which this power is produced is far from certain. Over the recent decades, several issues have arisen which has changed our perception of electricity. The most important issues are concerned with the environment and depleted fuel reserves.

The emission of greenhouse gases has found to be directly related to global warming, causing the earth to heat up. Fig.1.1 plots the steady increase of temperature over the last one hundred years or so and also shows a prediction of how temperatures will rise, dependent on what we as the human race do next. To simply stop using fossil fuels for electricity and transportation is implausible, but if we reduce the amount of fuel we burn we can at least suppress the effects of global warming. If we do not reduce our emissions, we could see a potential temperature increase of as much as 3.3°C (6°F).

Figure 1.1: Predicted temperature increase due to emissions [2]

The second and perhaps more immediate concern with fossil fuels is their long term supply. Put simply, we have an ever increasing demand for energy but a limited amount of fossil fuels from which we can produce this energy. Fig.1.2 shows the remaining amount of three commonly used fossil fuels. If we do not find alternative energy sources, in a little over 50 years from now we will exhaust our natural gas and crude oil supplies that are currently known to exist.

Figure 1.2: Fossil Fuels, years of extraction remaining [3]

The lower our reserves of fossil fuels become, the higher fossil fuel generated electricity prices will get. Presently, electricity in one form or another (being off-grid or on-grid) is accessible to 75% of mankind [4]. If we continue to rely upon the use of fossil fuels as our primary energy source, electricity prices will continue to rise until the poor can no longer afford it. The result would be millions of people and entire countries, particularly emerging economies, falling into energy poverty. Electricity provides the energy needed for manufacturing equipment, refrigeration for medical supplies, and energy for water treatment. It is therefore essential that alternative energy generation sources are found.

#### **1.3 Renewable Energy**

The alternative to fossil fuels is renewable or nuclear energy. Renewables are a source of energy that is replenishable and therefore everlasting. Worldwide directives have begun to emerge putting pressure on individual governments to reduce their dependency on fossil fuels, thereby reducing carbon emissions. Taking the United Kingdom as an example, the 2009 Renewable Energy Directive set a target for the UK to achieve 15% of its energy consumption from renewable sources by 2020 [5]. If the targets are not met there could well be financial sanctions imposed by other directive members. In recent years there has been a worldwide boom in renewable energy which is demonstrated in fig. 1.3. The figure also displays future predictions of energy usage by fuel type, indicating that we are only just entering the era of renewable energy, which is set to substantially increase by 2040. It is important to note that nuclear energy is often included as a renewable energy source as it does not produce carbon emissions. Strictly speaking however, nuclear energy is not truly renewable as uranium is required, and estimated uranium reserves will only last for another 80 years at the current usage rate [6]. Despite this, the use of nuclear energy is predicted to increase as shown in fig.1.3. Safety issues that have recently come to light (with the Fukushima nuclear disaster) could affect this prediction as public concerns over the technology escalate.

Figure 1.3: World energy consumption by fuel type 1990-2040 [1]

Types of truly renewable energy include those that produce electricity directly and those that need to be burnt to release energy. The main technologies are:

- 1. Direct electricity production

- Wind: Wind turbines harvest kinetic energy from the wind and convert this energy into electricity.

- Hydro: Hydro generators harvest kinetic energy from the movement of water and like wind turbines, convert this energy into electricity.

- Solar Photovoltaics: Solar cells convert the energy from sunlight into DC electricity.

- Ocean

- Tidal: Tidal generators can take various forms but all rely upon harnessing energy from the movement of water.

- Wave: Wave generators convert the up and down movement of waves into electrical energy.

- 2. Heat production

- Anaerobic digestion: The process of anaerobic digestion releases methane gas which can be burnt to provide heat.

- Bio energy

- Wood: Felled trees can be burnt to provide heat.

- Biomass: Vegetation can be burnt to provide heat.

- Biofuel: Fuels such as ethanol can be produced from crops of corn.

- Solar thermal: Different to solar PV, solar thermal uses energy from sunlight to heat water or other liquids.

- Geothermal: Harnesses the earth's geothermal energy by digging deep into the ground.

From the above list, some renewable technologies provide an alternative fuel source which must be burnt in order to release its energy. The burning of a fuel (even if it is renewable) releases carbon which pollutes the atmosphere. For zero emission energy production, harnessing energy from the earth is critical. Solar, wind, hydro, geothermal, tidal and wave are all zero carbon energy techniques that can provide our energy without contributing to global warming. Table.1.1 shows the current and a predicted future use of such renewable sources. From the table, hydroelectric and wind are predicted to continue to produce most of the renewable energy, but solar has the largest annual percent change of 9.1%.

| Region        | 2010  | 2015  | 2020  | 2025  | 2030  | 2035  | 2040  | Average annual<br>percent change,<br>2010-2040 |

|---------------|-------|-------|-------|-------|-------|-------|-------|------------------------------------------------|

| World         |       |       |       |       |       |       |       |                                                |

| Hydroelectric | 3,402 | 3,805 | 4,452 | 4.762 | 5,177 | 5,692 | 6,232 | 2.0                                            |

| Wind          | 342   | 767   | 1,136 | 1,383 | 1,544 | 1.694 | 1,839 | 5.8                                            |

| Geothermal    | 66    | 112   | 133   | 146   | 171   | 195   | 220   | 4.1                                            |

| Solar         | 34    | 157   | 240   | 288   | 327   | 394   | 452   | 9.1                                            |

| Other         | 332   | 427   | 549   | 643   | 729   | 800   | 858   | 3.2                                            |

| Total World   | 4,175 | 5,267 | 6,509 | 7,222 | 7,948 | 8,775 | 9,601 | 2.8                                            |

|               |       |       |       |       |       |       |       |                                                |

Table 1.1: Renewable electricity generation (billion kilowatt-hours) by energy source [1]

#### 1.4 Solar Energy

Solar renewable energy is typically split into two classifications, generation of heat and generation of electricity; technically referred to as solar thermal and solar photovoltaics respectively. This work will focus upon the use of solar photovoltaics for direct production of electricity.

In 1839, Edmund Becquerel discovered the photovoltaic effect [7] which is the basic principle by which solar photovoltaic cells operate. A solar cell converts energy from sunlight into electricity. The electricity produced by the solar cell is in the form of direct current (DC). Direct DC electricity production is unique to solar cells, with other renewable technologies such as wind and hydro power generating alternating current (AC).

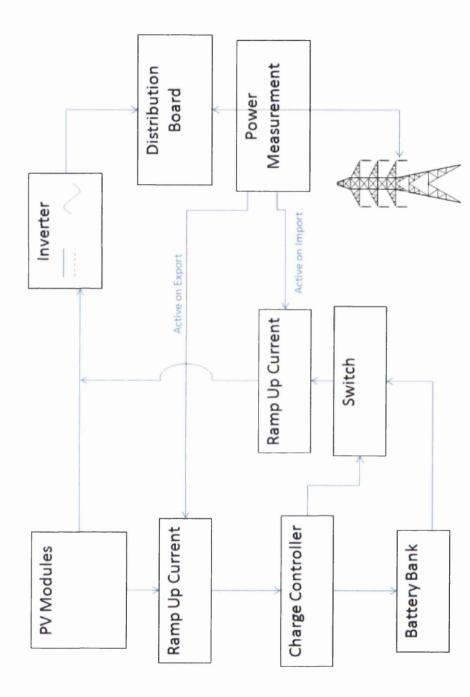

A single solar cell typically produces a very low voltage and therefore it is common for many solar cells to be connected together in series to provide a more useful, higher voltage. When cells are connected together to form a larger array, the product is known as a solar module or panel. Solar cells also produce direct current which for some applications is ideal, although most domestic appliances use alternating current. To convert the direct current produced by solar cells into an alternating current an electrical device called an inverter is used. An array of panels connected to an inverter forms the basics of a solar PV system, which is typically what is installed in domestic applications. More details on the system element of this technology can be found in the Appendix B of this work.

The use of solar photovoltaic renewable energy has grown exponentially over the last ten years as can be observed in fig.1.4.

Figure 1.4: Evolution of global PV cumulative installed capacity 2000-2012 (MW) [8]

The growth of the industry is due largely to two factors. Firstly the advantages of solar photovoltaics over other renewable technologies and secondly financial incentives offered by governments.

- 1. Advantages of solar photovoltaics over other renewable technologies:

- Zero carbon emissions

- Can work anywhere exposed to sunlight

- Not as obtrusive as wind turbines

- Virtually maintenance free as there are no moving parts

- Modular solar panels are used which allow for easy assembly of various size systems from Watts to Mega Watts.

- Ease of building integration due to the various sizes, colours and flexibility of cells available.

- Direct current (DC) generation allowing for simple battery storage systems.

- 2. Financial incentives. To boost the market for renewable technology, incentives have been offered for the installation of not only solar but also other renewable technologies. Focusing on the case of solar in the United Kingdom gives a good description of the incentives that have been offered. In 2010, the UK government introduced the Feed-In Tariff (FiT) to promote the installation of small scale renewable energy systems. As renewable technologies were seen by most as an unknown, the FiT provided a financial incentive for people to install them. The tariff is scaled depending on the size of such a system and guaranteed for between 20 and 25 years. Table.1.2 shows the first tariff incentives for solar electricity production (2010).

| Description            | 2010 Tariff (p/kWh) |  |  |  |

|------------------------|---------------------|--|--|--|

| <4kW new build         | 37.8                |  |  |  |

| <4kW existing building | 43.3                |  |  |  |

| 4kW - 10kW             | 37.8                |  |  |  |

| 10kW - 50kW            | 32.9                |  |  |  |

Table 1.2: 2010 UK solar feed in tariff [9]

The introduction of the tariff scheme saw a huge boost in solar PV installations in the UK. The downside to this was that the government had underestimated global PV system costs, which began to decrease rapidly. The financial incentive of the FiT had fast become a way for consumers of installed systems to make large profits. The typical payback time for a system was as low as five years meaning that the next 15 years of FiT payments were pure profit. On April 1<sup>st</sup> 2012, the UK government slashed the feed in tariff rates by 50% to prevent such profit making. The UK FiT for a <4kW PV system on an existing building (at the time of writing this thesis) is 14.9p/kWh.

#### **1.5 Solar Cell Generations**

Since the first silicon solar cell was produced at Bell Laboratories in the 1950's [10], there have been three generations of photovoltaic technologies. Fig.1.5 shows the most recent efficiency chart for all the different generations of solar cells.

1. First generation solar cells include the one fabricated at Bell Laboratories. These are wafer based silicon solar cells. Despite being the first generation of cells, they are the most commonly used type of silicon solar cell making up over 80% of the total PV market [11]. First generation cells can be further classified by the quality of the silicon they are fabricated from. There are two main categories namely monocrystalline and multicrystalline wafers. Monocrystalline cells are fabricated from high quality single crystal wafers, whereas multicrystalline cells are fabricated from wafers with multiple crystal domains. Due to the higher quality of monocrystalline cells, they have a higher efficiency than cells produced from multicrystalline substrates. Unfortunately such purity of monocrystalline cells comes at a cost and despite multicrystalline cells having lower efficiencies; they are more commonly used due to their lower production cost. From fig.1.5 wafer based silicon solar cells have achieved up to 25% efficiency (without concentration).

- 2. Second generation solar cells are known as thin film cells due to their thin solar active layers. Such cells include amorphous silicon (a-Si), Cadmium Telluride/Cadmium Sulfide (CdTe/CdS), Copper Indium Selenide and Copper Indium Gallium Selenide (CIGS) solar cells. Thin film second generation cells have lower efficiencies to that of first generation wafer based cells, but can be fabricated at low cost. Due to the materials and substrates used for such devices, solar cell production can take place over far larger areas than that of a typical wafer based cell. From fig.1.5, the highest performing technology in this generation are Copper Indium Gallium Selenide cells with 20.8% efficiency (without concentration).

- 3. Third generation solar cells typically do not rely on p-n junctions and can be of varied constructions. Third generation cells include nanostructured cells, organic PV OPV), dye-sensitised solar cells (DSSC), tandem/multijunction cells and concentrator cells. This wide ranging category offers cells that are cheap to produce with very low efficiencies, all way up to expensive cells offing very high efficiency such as the record efficiency three junction cell with 38.8% (without concentration) and 44.4% (under concentration at 302 suns) efficiencies. Concentrator cells use focused (concentrated) sunlight up to 1000x normal intensity.

- 6 -

#### 1.6 The Future of Photovoltaic Solar Cells

Wafer based silicon photovoltaics have dominated the photovoltaic industry since the very beginning of the solar cell market in the 1950's [13]. Other than wafer based crystalline cells, the rest of the terrestrial PV market is made up of thin film cells such as amorphous silicon (a-Si), cadmium-telluride (CdTe) and copper indium gallium selenide (CIGS) [14].

Despite the current market conditions, other cell technologies are predicted to gain a larger market share. Fig.1.6 shows some of the emerging technologies and their longterm predicted efficiencies.

|                                                 | 2010                                             | 2015-2020  | 2030- |  |  |

|-------------------------------------------------|--------------------------------------------------|------------|-------|--|--|

| CPV                                             |                                                  |            |       |  |  |

| Effic.(lab-effic),%                             | 20-25 (40)                                       | 36 (45)    | >45   |  |  |

| Major R&D areas and targets                     | lifetime; optical efficiency (85%), sun-         |            |       |  |  |

|                                                 | tracking, high concentration, up-scaling;        |            |       |  |  |

| Inorganic TF (spherical cells, poly c-Si cells) |                                                  |            |       |  |  |

| Effic.(lab-effic),%                             | (10.5)                                           | 12-14 (15) | 16-18 |  |  |

| Major R&D areas and targets                     | deposition, interconnection, ultra-thin films;   |            |       |  |  |

|                                                 | up-scaling, light tailoring                      |            |       |  |  |

| Organic cells (OPV, DSSC)                       |                                                  |            |       |  |  |

| Effic.(lab-effic),%                             | 4 (6-12)                                         | 10 (15)    | na    |  |  |

| Major R&D areas and targets                     | Lifetime (>15 yr), industrial up-scaling         |            |       |  |  |

| Novel active layers                             |                                                  |            |       |  |  |

| Effic.(lab-effic),%                             | na                                               | (>25)      | 40    |  |  |

|                                                 | Materials, deposition techniques,                |            |       |  |  |

| Major R&D areas and targets                     | understanding quantum effects, up-scaling        |            |       |  |  |

|                                                 | from lab production                              |            |       |  |  |

| Up/down converters                              |                                                  |            |       |  |  |

| Module effic., %                                | +10% over ref material                           |            |       |  |  |

| Major R&D areas and targets                     | (nano) materials, physical stability, up-scaling |            |       |  |  |

Figure 1.6: Performance and targets for emerging PV options [14]

Concentrated photovoltaics (CPV) have existed for many years although they have still not broken into the mainstream solar cell industry, mainly because of high costs associated with the technology. Their primary application therefore has been in high value markets such as power generation for space applications [11]. Wafer based silicon solar cells have shown promise at relatively low concentration ratios, but the heat generated by high concentrator systems begins to degrade cell performance (as much as -0.5% relative per °C [11]). The materials of choice for high concentrator system are III-V semiconductors which can be tailored to produce a wide range of optical band gaps. Multijunction cells fabricated from various III-V materials can further utilise the whole solar spectrum. As previously described above, triple junction (GaInP/GaInAs/Ge) cells have produced record breaking efficiencies of 44.4% at 302x light concentration. Cost reductions relating to cell manufacture and optical tracking for concentrator lenses, could see the technology commercially used.

Inorganic thin film (TF) solar cells such as a-Si, CIS, CIGS and CdTe already have a 20% market share [14], but their relatively low cell efficiencies are limiting mainstream use relative to crystalline silicon cells. It is important to note however that there has been a large amount of interest in recent years regarding thin film cells. Many analysts predicted that the price per watt of thin film technologies would by now be far less than that of wafer based silicon cells. However, the recent market trend for wafer based cells (which is discussed in more detail in 1.7) has seen the opposite effect as can be observed in fig.1.7.

Dec-09 Mar-10 Jun-10 Sep-10 Dec-10 Mar-11 Jun-11 Sep-11 Dec-11 Mar-12 Jun-12 Sep-12 Dec-12 Figure 1.7: Chinese manufacturer average panel price for thin film and crystalline silicon [15]

From fig.1.7 it is apparent that until the middle of 2011, thin film solar cells were significantly cheaper than crystalline silicon based modules. It is quite possible that in the future, cost reductions and efficiency improvements will continue to be made in thin film technology at a faster rate than that of crystalline silicon equivalents.

Thin film cells such as dye sensitised and organic PV (OPV) cells can feasibly achieve a cost per watt of below \$0.50 (USD) once scaling of processes is applied [14]. Issues around relatively low efficiency (11% academic record) and lifetime issues related to dye sensitised solar cells (DSSCs) are currently holding back the technology, although advancements through extensive research are continually being made. If lifetime and commercial efficiencies can be raised, organic cells, due to their inherent low cost and large scale application could have a large impact on the solar industry, although there are still significant obstacles to overcome.

There are many novel solar cell technologies constantly being developed and analysed. The interest in nanotechnology has seen a wide range of different structures and materials than can have excellent absorption capabilities as well as theoretical efficiency limits as high as 60% [14]. Another significant recent breakthrough has been the use of perovskite for cell production, which stemmed from research into DSSCs. Perovskites are the name given for any materials that have the same crystal structure as calcium titanate, hence they are abundant materials [16]. The technology has seen research investigations in the last year with cells rapidly reaching conversion efficiencies in excess of 15% [17]. Such cells although still firmly in the research and development phase are predicted to be capable of reaching efficiencies as high as 20-25% and cost only \$0.10 to \$0.20 (USD) per watt [18].

Despite the research and development of several different solar cell technologies, it is safe to say that for the foreseeable future, crystalline silicon solar cells will continue to dominate the market as they have done for over 50 years. A significant amount of research still revolves around efficiency enhancement and cost reduction of wafer based silicon solar cells. Recent research into up and down converters for example aims for photon absorption and re-emission at a different wavelength which could improve the efficiency of silicon solar cells by up to 10% (by expanding the spectral range of absorption) [14]. Laboratory developed silicon solar cells are now reaching in excess of 25% and moving ever closer to the theoretical silicon solar cell efficiency limit of 29.8% [19].

Of all PV technologies, perovskite sensitised solar cells have the greatest potential for replacing silicon wafer based cells, provided that predictions of cost and efficiency prove to be correct. The shear abundance of the material and simple processing technology (low cost), coupled with efficiencies as high as 25% could revolutionise the industry and help photovoltaic generated electricity to contend financially with fossil fuel technologies.

#### **1.7 Cost Vs Efficiency**

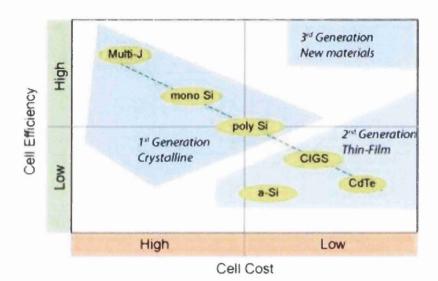

The commercial success of a solar cell technology not only relies upon efficiency but also the cost of producing the cell. Wafer based silicon solar cells dominate the market despite only being around 18-20% efficient. The reason they are so successful is that they provide reasonable electrical power at low cost. These parameters are critical for commercial installations of PV where people are competing directly against the cost of other renewable and fossil fuel technologies. For niche applications where cost is not as significant, high efficiency cells can be used for their higher electrical output, for example III-V solar cells for satellite applications. Fig.1.8 shows the typical efficiency and cost implications of each of the solar cell generations.

Figure 1.8: Efficiency Cost Profile for different solar generations [20]

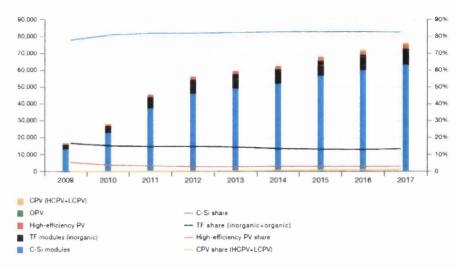

Despite the low efficiency of wafer based crystalline silicon cells compared to multijunction cells that can exhibit efficiencies in excess of 40%, silicon cells dominate the market place. Fig. 1.9 shows the current and predicted market share of photovoltaics by each technology type. The market share of silicon is predicted to remain constant at around 80% until 2017 at least. The reason for the great success of silicon is due to its abundance of raw materials, reliability, ease of construction, and wealth of knowledge in the area taken from the semiconductor industry. Industrial equipment specifically designed for silicon solar cell production has long been used and adopted by many countries that are now able to produce vast quantities of cells at low cost. The production of silicon specifically for solar cell production also greatly enhanced mass production capability resulting in huge cost reductions.

Figure 1.9: Market share of photovoltaics by each technology type [8]

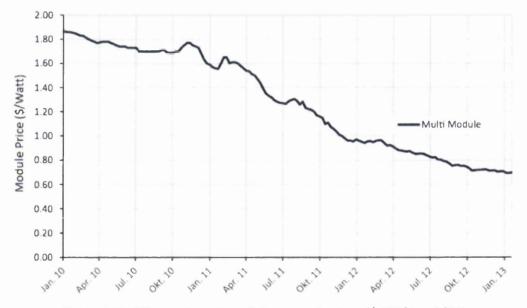

Such large scale manufacturing of solar cells and panels particularly in China, has in recent years, led to a huge fall in the cost of silicon wafer based solar cells. The extent of the dramatic fall in panel costs is shown in fig.1.10, with a cost per watt of \$1.81 in the first quarter of 2010 which reduced significantly to just \$0.70 at the beginning of 2013.

Figure 1.10: Silicon solar cell module cost reductions (\$USD/Watt) [21]

It is important to note that these price reductions do not entirely translate into streamlining of the industry. Chinese cell manufacturers have been reported to be producing and selling solar cells and modules below cost [22]. This is mainly due to oversupply issues in the Chinese solar industry with production of cells exceeding demand. Recently due to the adverse effect of such 'dumping' of below cost modules, the European Union imposed a series of measures on Chinese imported cells and modules. The measures included limiting EU imports to 7GW annually and also setting a minimum price of  $\notin 0.56$  per watt for silicon based modules [23]. Despite the minimum pricing, the majority of European solar module manufacturers have said that the pricing is still far too low and actual cost of solar production in China [24].

The turbulence in the industry has put a larger emphasis on cost reduction than ever before. Put simply, without substantial cost reductions or further government intervention, European solar cell manufacturers will continue to find it very hard to compete in the market. Recently here in the United Kingdom Sharp has announced the closure of its solar panel assembly plant because it is unable to compete in the current market [25].The UK industry now has to develop intellectual property and niche PV products (high value) to survive in the current market.

The focus of solar photovoltaics has always been strongly influenced by efficiency and cost. In order for the industry to continue to impact upon the renewable energy market, cell efficiency will need to rise or costs will need to reduce or preferably a combination of both. Unfortunately however, a trade-off currently exists between these two factors.

#### **1.8 Outline of Thesis**

Wafer based silicon solar cells dominate the market due to their reasonably high efficiencies and low cost processing conditions. In order for wafer based silicon solar cells to continue to dominate the market, they must continue to increase in efficiency whilst reducing in cost. As the efficiency of lab based silicon cells are approaching the fundamental limit for such devices, cost factors are becoming more important.

The primary aim of this work is to target the material usage for cell production. It will be shown that current wafer based silicon solar cells are using far more silicon material than is actually required for high efficiency cells. The cost of conventional monocrystalline solar cells is relatively high because of the high purity of the silicon wafer substrate from which the cell is produced. By producing a cell that uses less silicon material, significant cost savings can be made. Conventional techniques used in industry to produce cells are limited by the thickness of which a substrate can be cut. The method adopted and investigated in this work uses exfoliation principles to produce silicon substrates only 40µm thick. Such thin silicon foils are more than four times thinner than that currently used to fabricate commercial solar cells. The work investigated a variety of principles related to the process, in order to optimise and understand the mechanisms involved. From the experimental research, a novel process was developed in order to fabricate a fully operational solar cell from the40µm thick silicon foil.

One significant issue that arose from the use of such a thin exfoliated silicon substrate was the difficulty of using conventional anti-reflective texturing techniques. Such microscale texturing could significantly weaken the structure of a thin (40µm) silicon substrate. Issues relating to the surface quality of exfoliated Si substrates could also potentially disrupt effectiveness of conventional anisotropic texturing techniques. Research was conducted into finding an alternative technique to match the performance of commercially used anti reflective processes. Experiments into the formation of porous silicon on the surface of a silicon substrate were found not only to match the commercial process, but to exceed the antireflective performance of conventional ARCs. The technique was deemed to be suitable for both thick crystalline and thin crystalline silicon wafer based substrates. The PSi layer was also found to have the potential to reduce costs associated with front surface reflectivity suppression, by using a single etching process. Using such a simple technique to provide reflectivity suppression could be more economical compared to the two step conventional technique commercially adopted.

Experimental investigation also focused upon the top contact for wafer based silicon solar cells. As the top of the cell must allow for light absorption and the formation of electrical contacts, a trade off exists between shading losses and resistance of the front metallisation. A method was adopted to increase the electrical performance of standard front contact topologies without significantly increasing shading loss. Silver nanowires were successfully deposited and analysed on standard silicon solar cell top contacts as an electrical enhancement contact. Such a coating can improve the collection ability of the top contact but due to their nanoscale diameters, shading losses are not dramatically increased by the silver nanowires. The coating resulted in a substantial increase in cell efficiency when the optimum nanowire coating density layer was applied. The silver nanowire contact scheme is not compatible with traditional micro textured anti reflective surface. However, it can be integrated with the porous silicon anti reflective method developed in this work.

As my work was part funding by a solar cell fabrication company, product development was also undertaken. Although this work was not strictly academically based, it provided me with a commercial insight into the integration of photovoltaics with our environment. Two silicon solar cell based products that I helped to develop in conjunction with the company, have been briefly outlined in the Appendices Chapter of this work.

- [1] Energy Information Administration, International Energy Outlook 2013, EIA, 2013

- [2] Epa.gov. 2013. Future Climate Change | Climate Change | US EPA. [online] Available at: http://www.epa.gov/climatechange/science/future.html [Accessed: 4 Dec 2013]

- [3] Knoema. 2013. World Reserves of Fossil Fuels knoema.com. [online] Available at: http://knoema.com/smsfgud/world-reserves-of-fossil-fuels [Accessed: 4 Dec 2013]

- [4] International Energy Agency, World Energy Outlook 2009, IEA, 2009

- [5] Gov.uk. 2012. Increasing the use of low-carbon technologies Policy GOV.UK. [online] Available at: https://www.gov.uk/government/policies/increasing-the-useof-low-carbon-technologies [Accessed: 4 Dec 2013]

- [6] Royalsociety.org. 1999. Nuclear energy the future climate | Royal Society. [online] Available at: http://royalsociety.org/policy/publications/1999/nuclear-energy/ [Accessed: 9 Aug 2013].

- [7] Luque, A.; Hegedus, S., Handbook of Photovoltaic Science and Engineering, John Wiley & Sons, 3 -312, 2003

- [8] European Photovoltaic Industry Association, Global Market Outlook for Photovoltaics, 2013-2017, EPIA, 2013

- [9] Ofgem.gov.uk. 2013. Feed-in Tariff Table 1 August 2011 | Ofgem. [online] Available at: https://www.ofgem.gov.uk/publications-and-updates/feed-tariff-table-1august-2011 [Accessed: 2 Nov 2013].

- [10] D.M. Chapin, C.S. Fuller and G.L. Pearson, A new p-n junction photocell for converting solar radiation into electrical power, J. Applied Phys. Vol 25, 1954, pp.: 676-677, 1954

- [11] Luque, A.; Hegedus, S., Handbook of Photovoltaic Science and Engineering, Second Edition, John Wiley & Sons, 265-313, 2011

- [12] National Renewable energy Laboratory, Efficiency Chart, NREL, Rev 12-04-2013

- [13] Comprehensive Renewable Energy, Ali Sayigh, Oxford Elsevier, 2012

- [14] IEA-ETSAP and IRENA© Technology Brief E11 January 2013

- [15] CleanTechnica. 2013. panel\_price\_en. [online] Available at: http://cleantechnica.com/2013/01/13/small-chinese-solar-manufacturers-weredecimated-in-2012/panel\_price\_en/ [Accessed: 22 Nov 2013].

- [16] Henry J. Snaith, Perovskites: The Emergence of a New Era for Low-Cost, High-Efficiency Solar Cells, The Journal of Physical Chemistry Letters, 4 (21), 3623-3630, 2013

- [17] Docampo, Pablo *et al*, Efficient organometal trihalide perovskite planarheterojunction solar cells on flexible polymer substrates, Nature Communications 4, 2761, 2013

- [18] MIT Technology Review. 2013. A Material That Could Make Solar Power "Dirt Cheap" | MIT Technology Review. [online] Available at: http://www.technologyreview.com/news/517811/a-material-that-could-makesolar-power-dirt-cheap/ [Accessed: 22 Dec 2013].

- [19] Tiedje, T.; Yablonovitch, E.; Cody, G.D.; Brooks, B.G., "Limiting efficiency of silicon solar cells," Electron Devices, IEEE Transactions, vol.31, no.5, pp.711-716, 1984

- [20] Greenrhinoenergy.com, (2014). PV Cells & Modules, Photovoltaics | Solar Power.

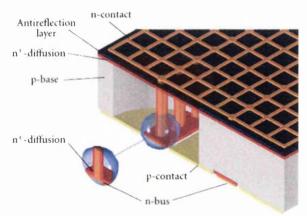

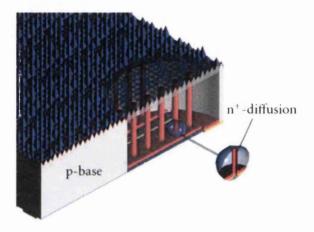

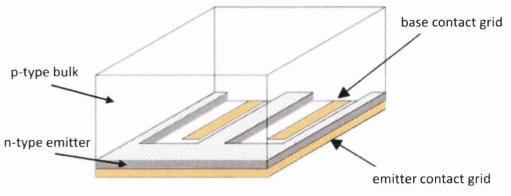

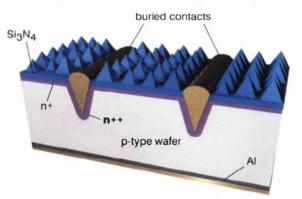

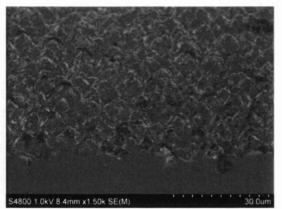

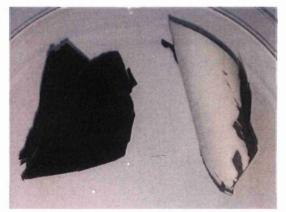

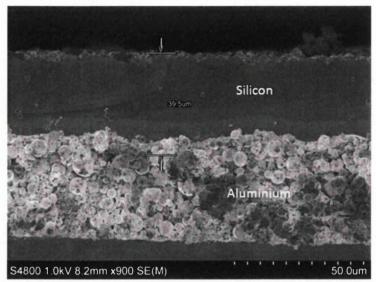

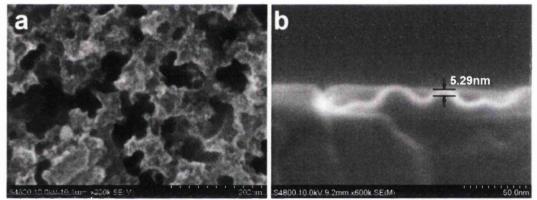

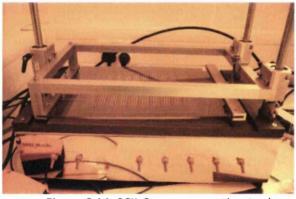

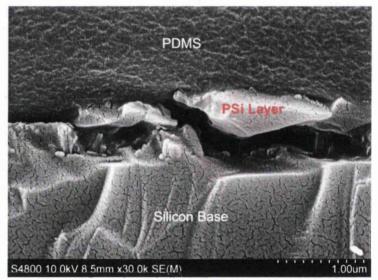

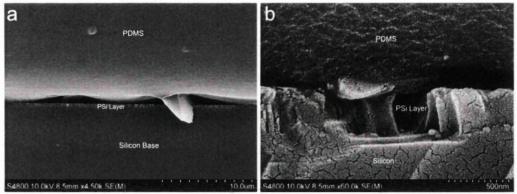

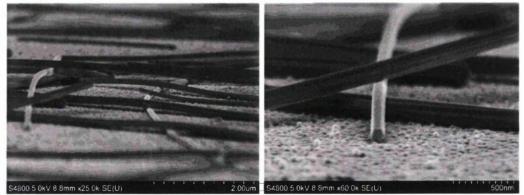

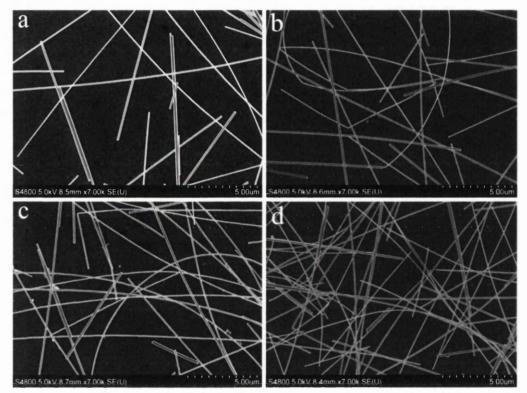

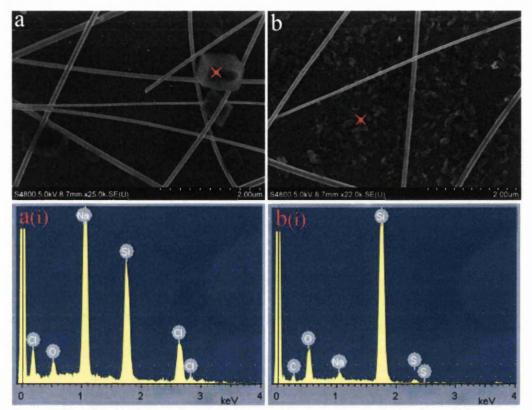

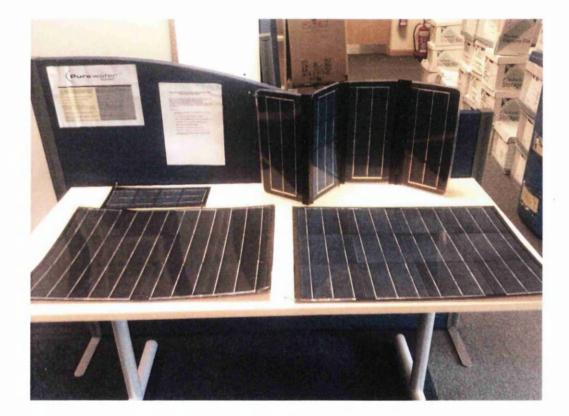

[online] Available at: http://www.greenrhinoenergy.com/solar/technologies/pv\_modules.php [Accessed 19 May. 2014].