Investigation into the manipulation of nonuniformity and undercut features of a positive profile through silicon via.

# Paul Gray

Submitted to Swansea University in fulfilment of the requirements for the Degree of Doctor of Philosophy

Swansea University

2022

# **Summary**

The key enabling technology for 2.5D and 3D packaging applications is the through silicon via (TSV), this device allows integrated circuits and additional component layers to be vertically stacked, this minimises internal signalling lengths allowing for faster operation, reduced heat production and lower power consumption.

TSV's are commonly formed with a positive profile structure which minimises conductor deposition defects in downstream production stages. This research was carried out on an SPTS Technologies Ltd Pegasus<sup>TM</sup> deep silicon etcher employing a single step O<sub>2</sub>/SF<sub>6</sub>/Ar process. The aim was to identify a predictable set of process parameters that can be used manipulate the dimensions of the 'undercut' feature that regularly forms at the top of the TSV profile during dry plasma etch processing.

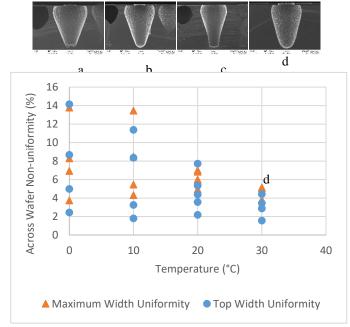

An L16 (4^5) Taguchi Array was used to determine the interaction effects of changing five critical process parameters on the undercut feature dimensions. The results from the process sample runs were analysed using commercially available statistical analysis software to investigate any predictable interactions between process parameter values and TSV profile dimensions. The outcome showed that there were no relationships that would facilitate predictable manipulation of the undercut dimensions. However, a clear and predictable trend was observed from the results which showed that increasing the wafer platform temperature results in a decrease in across wafer non-uniformity of critical TSV profile dimensions.

### **Declarations**

#### **Declarations**

This work has not previously been accepted in substance for any degree and is not being concurrently submitted in candidature for any degree.

Signed

Date: 10/12/2021

This thesis is the result of my own investigations, except where otherwise stated. Other sources are acknowledged by footnotes giving explicit references. A bibliography is appended.

Signed

Date: 10/12/2021

I hereby give consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside organisations.

Signed

Date: 10/12/2021

The University's ethical procedures have been followed and, where appropriate, that ethical approval has been granted.

Signed

Date: 10/12/2021

# Contents

| Summary                                       | 1  |

|-----------------------------------------------|----|

| Declarations                                  | 2  |

| Acknowledgements                              | 7  |

| List of Figures                               | 8  |

| List of Tables                                | 12 |

| Definitions or Abbreviations                  | 15 |

| Chapter Content Descriptions                  | 16 |

| Chapter 1 - Introduction                      | 17 |

| 1.1 Integrated Circuit History                | 18 |

| 1.2 2.5 D and Beyond                          | 22 |

| 1.3 Integrated Circuit Packaging Types        | 23 |

| 1.5 TSV Construction                          | 26 |

| 1.6 TSV Profile Undercut Formation            | 29 |

| 1.7 Two Stage Undercut Removal Method         | 32 |

| 1.8 Current Research on Undercut Manipulation | 34 |

| 1.9 Scope of the Research                     | 36 |

| Chapter 2 - Methodology                       | 37 |

| 2.1 Objectives of the Research                | 38 |

|     | 2.2 Photolithography                                                           | 39 |

|-----|--------------------------------------------------------------------------------|----|

|     | 2.3 Selection of substrate material and mask pattern                           | 40 |

|     | 2.4 Substrate Etching                                                          | 43 |

|     | 2.5 Dry Plasma Etching                                                         | 51 |

|     | 2.6 Scanning Electron Microscope (SEM)                                         | 57 |

|     | 2.7 Measurement Techniques Employed to Characterise the Etch Performance       | 62 |

|     | 2.8 Etch Hardware                                                              | 66 |

|     | 2.9 Etch Process Steps                                                         | 69 |

|     | 2.10 Etch Process Parameter Trends                                             | 73 |

|     | 2.11 Design of Experiments (DoE)                                               | 77 |

|     | 2.12 DOE Run Parameters                                                        | 78 |

|     | 2.13 Profile Characterisation                                                  | 80 |

|     | 2.14 Measurement Locations                                                     | 83 |

|     | 2.15 Sample Measurement                                                        | 84 |

|     | 2.16 Analysis Method                                                           | 85 |

| Cha | apter 3 – Results                                                              | 87 |

|     | 3.1 Run 1: (Starting process)                                                  | 90 |

|     | 3.2 Run 2: (- gas flow - coil RF - platen RF - pressure - platen temperature)* | 91 |

|     | 3.3 Run 3: (= gas flow + coil RF + platen RF + pressure + platen temperature)* | 92 |

|     | 3.4 Run 4: (= gas flow + coil RF + platen RF + pressure + platen temperature)* | 93 |

|     | 3.5 Run 5: (= gas flow + coil RF + platen RF + pressure + platen temperature)* | 94 |

| 3.6 Run 6: (+ gas flow - coil RF - platen RF - pressure = platen temperature)*95    |

|-------------------------------------------------------------------------------------|

| 3.7 Run 7: (= gas flow + coil RF - platen RF + pressure - platen temperature)*96    |

| 3.8 Run 8: (= gas flow + coil RF + platen RF - pressure - platen temperature)*97    |

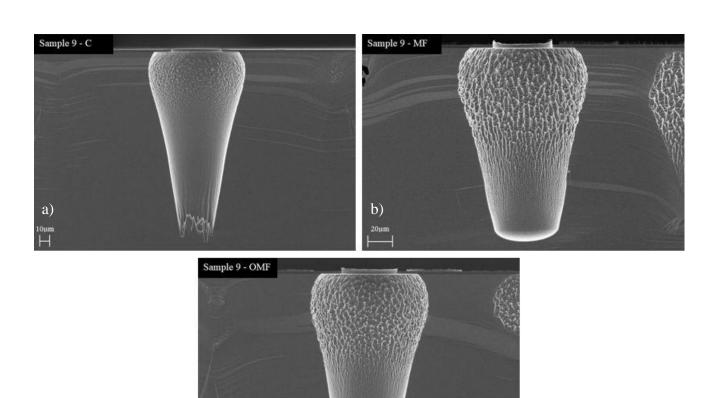

| 3.9 Run 9: (= gas flow + coil RF - platen RF + pressure - platen temperature)*98    |

| 3.10 Run 10: (+ gas flow - coil RF = platen RF + pressure + platen temperature)99   |

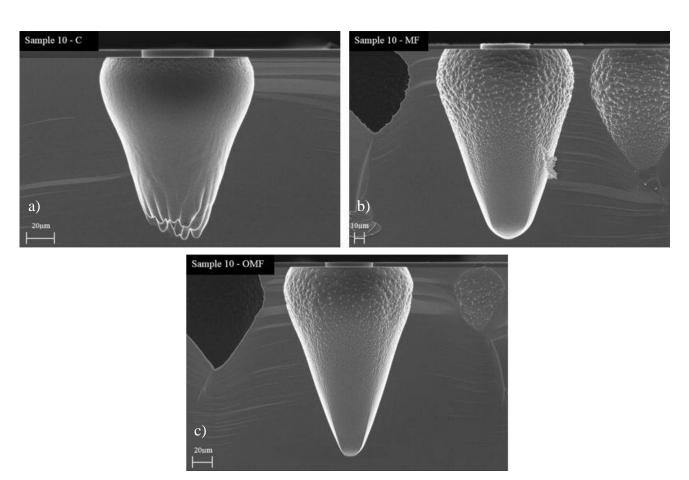

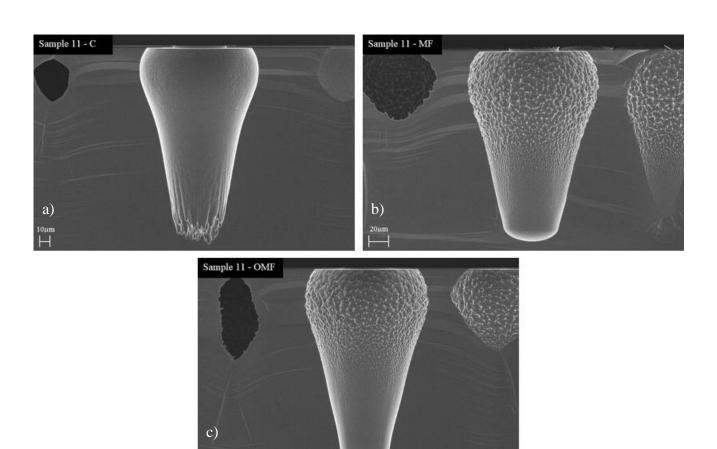

| 3.11 Run 11: (= gas flow + coil RF + platen RF - pressure - platen temperature)*100 |

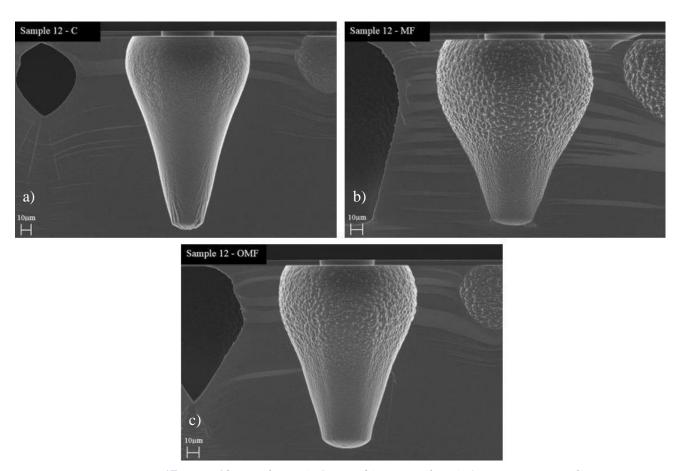

| 3.12 Run 12: (= gas flow + coil RF - platen RF - pressure + platen temperature)*101 |

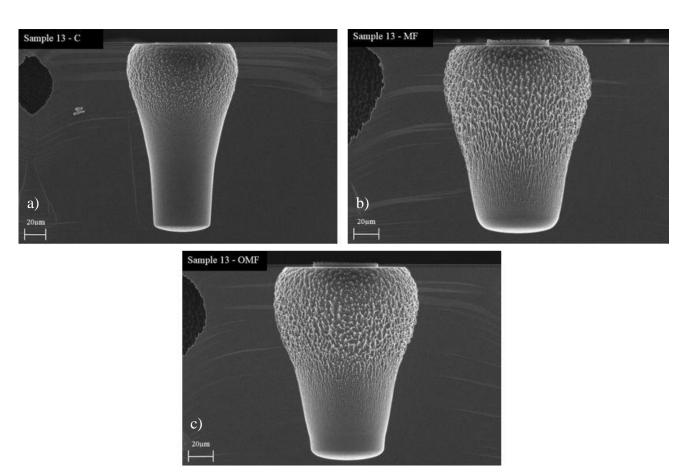

| 3.13 Run 13: (= gas flow + coil RF + platen RF - pressure - platen temperature)*102 |

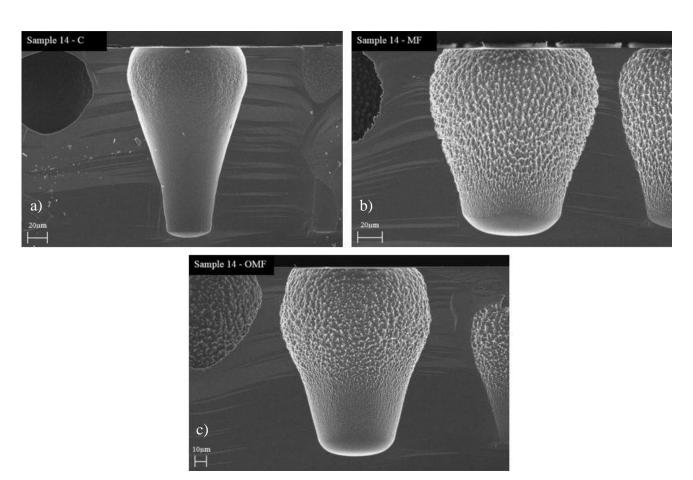

| 3.14 Run 14: (+ gas flow - coil RF + platen RF + pressure = platen temperature)*    |

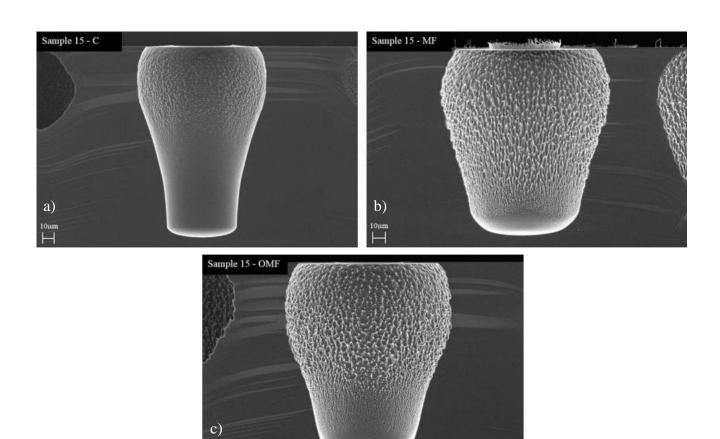

| 3.15 Run 15: (= gas flow + coil RF - platen RF - pressure + platen temperature)104  |

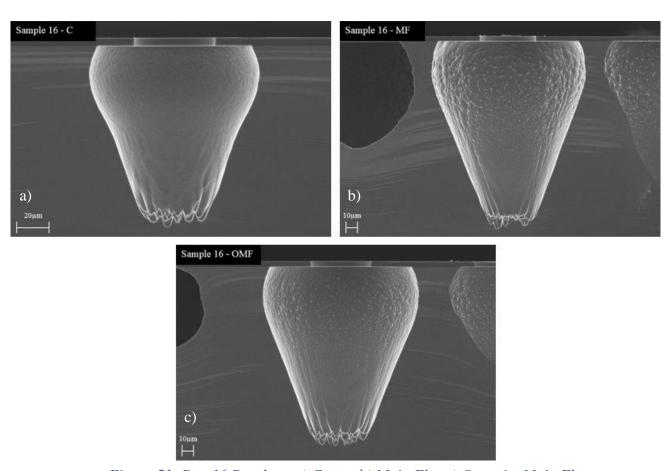

| 3.16 Run 16: (= gas flow + coil RF - platen RF + pressure - platen temperature)*105 |

| 3.17 Run 17: (= gas flow + coil RF - platen RF - pressure + platen temperature)*106 |

| 3.18 Results Analysis Interpretation                                                |

| 3.19 Results Analysis                                                               |

| Chapter 4 – Computer Modelling                                                      |

| 4.1 Substrate Platform Cooling Simulation                                           |

| 4.2 Cooling Simulation Results                                                      |

| Chapter 5 - Conclusions                                                             |

| 5.1 Process Parameter Effect on the Undercut                                        |

| 5.2 Data Trend Summary                                                              |

| 5.3 Further Work                                                                    |

| Bibliography                 | 141 |

|------------------------------|-----|

| Chapter 6 – Research Paper   | 145 |

| Appendix                     | 152 |

| 1. Sample Process Run Notes: | 152 |

## Acknowledgements

I wish to thank Dr Lijie Li, my supervisor at Swansea University for his help, guidance, and support during the preparation of this thesis.

I would like to thank Dr Huma Ashraf and Dr Janet Hopkins who acted as mentors during this process, and my employer SPTS Technologies who kindly gave me the resources to complete this work.

Very special thanks must go to Dr Nigel Davies as without his support and encouragement this document would never have been started.

For Sarah, Ethan, Rory, and Jacob

# **List of Figures**

|    | Figure 1: Traditional CPU/RAM                                                  | 23 |

|----|--------------------------------------------------------------------------------|----|

|    | Figure 2: CPU/RAM in a single package (2.5D)                                   | 23 |

|    | Figure 3: True 3D IC Package                                                   | 24 |

|    | Figure 4: Samsung DDR4 DRAM Memory Stack (Source: Samsung 3D TSV, Stacked DDR4 |    |

| DI | RAM report – System Plus Consulting, 2015.)                                    | 25 |

|    | Figure 5: Typical TSV (via middle) Manufacturing Process                       | 27 |

|    | Figure 6: TSV Feature Profiles [25]                                            | 29 |

|    | Figure 7: TSV Overhang, a) Centre position, b) Edge position                   | 30 |

|    | Figure 8: Overhang Shadowing Effect                                            | 31 |

|    | Figure 9: Typical overhang process flow removal process [31]                   | 32 |

|    | Figure 10: Effect of Mask Profile on Undercut [26]                             | 35 |

|    | Figure 11: Photolithography Process [39]                                       | 40 |

|    | Figure 12: Test Wafer Layout (copied with permission of SPTS Technologies)     | 42 |

|    | Figure 13: Isotropic Etch Profile [45]                                         | 43 |

|    | Figure 14: Anisotropic Etch Profile [45]                                       | 43 |

|    | Figure 15: Positive Etch Profile [46]                                          | 44 |

|    | Figure 16: Matter State Vs Temperature [49]                                    | 46 |

|    | Figure 17: Ionisation of a gas molecule within a plasma reactor                | 47 |

|    | Figure 18: Excitation-relaxation photon emission                               | 48 |

|    | Figure 19: Dissociation by electron impact                                     | 49 |

|    | Figure 20: Typical SPTS Plasma Etch ICP System                                 | 51 |

|    | Figure 21: Etching Types and the Resulting Profiles (a) Chemical etching by fluorine radical       | s, (b) |

|----|----------------------------------------------------------------------------------------------------|--------|

| Ph | aysical etching by SF <sub>6</sub> ions, (c) Positive profile resulting from combined etching [46] | 54     |

|    | Figure 22 Scanning Electron Microscope Block Diagram                                               | 58     |

|    | Figure 23: Positive Profile Measurement [25]                                                       | 63     |

|    | Figure 24: Negative Profile Measurement [25]                                                       | 64     |

|    | Figure 25: Vertical Profile Measurement [25]                                                       | 64     |

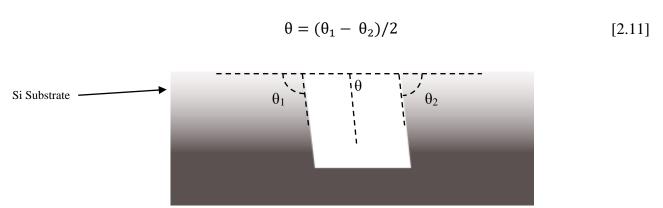

|    | Figure 26: Profile Tilt Measurement.                                                               | 65     |

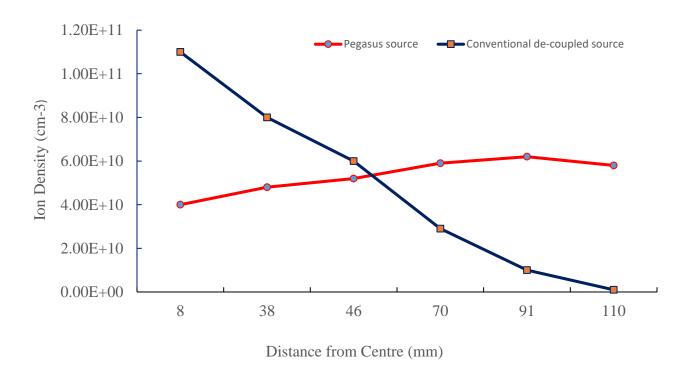

|    | Figure 27: An SPTS Pegasus System® (copied with permission of SPTS Technologies)                   | 67     |

|    | Figure 28: SPTS Pegasus Plasma Uniformity (reproduced with permission of SPTS                      |        |

| Te | echnologies)                                                                                       | 67     |

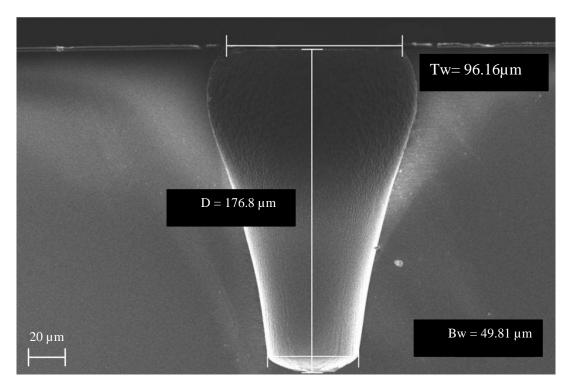

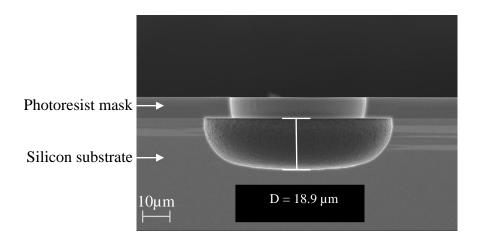

|    | Figure 29: Initial Etch Process Test Result (centre)                                               | 72     |

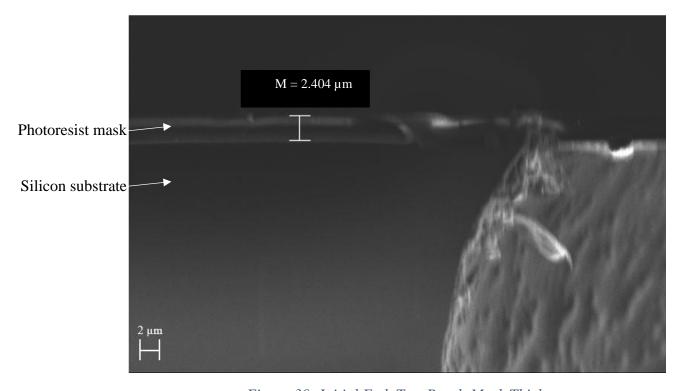

|    | Figure 30: Initial Etch Test Result Mask Thickness                                                 | 72     |

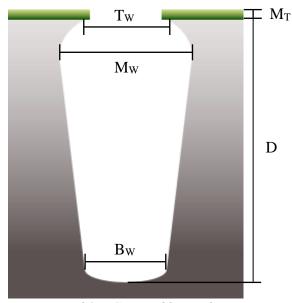

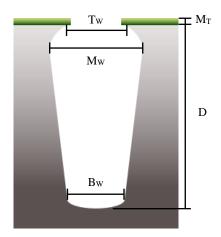

|    | Figure 31: TSV Profile Explanation                                                                 | 80     |

|    | Figure 32: Failed Process Test                                                                     | 82     |

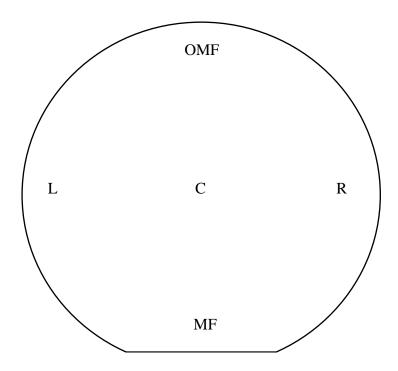

|    | Figure 33 Measurement Locations.                                                                   | 83     |

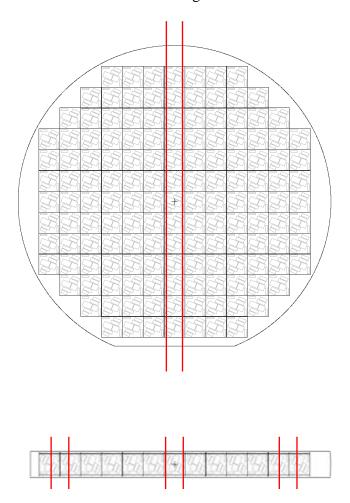

|    | Figure 34 Processed Wafer Cleave Positions                                                         | 84     |

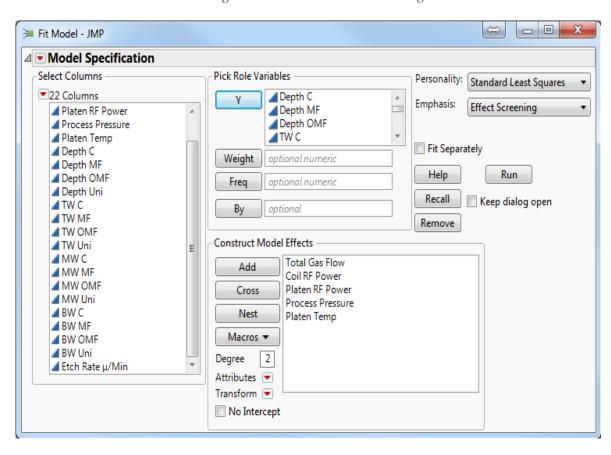

|    | Figure 35: JMP Fit Model settings                                                                  | 87     |

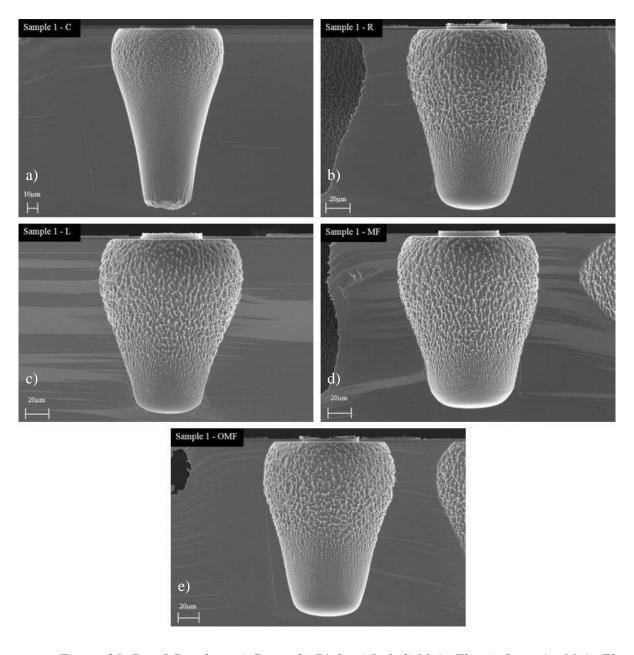

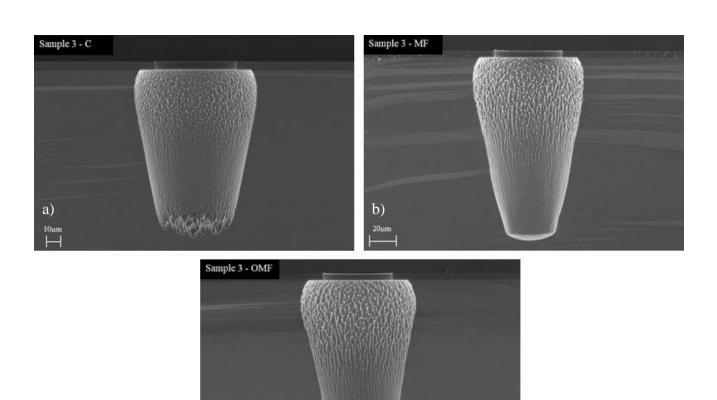

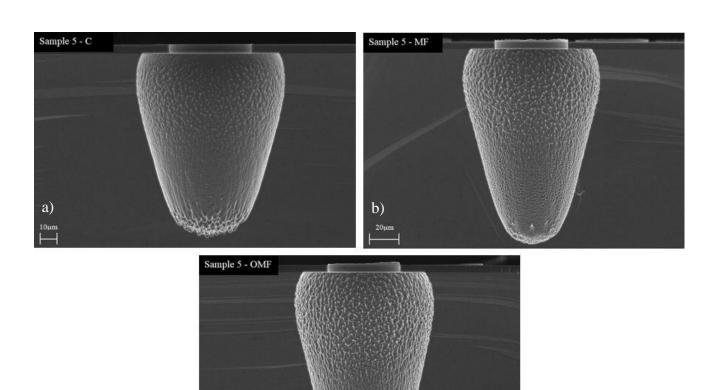

|    | Figure 36: Run 1 Results - a) Centre b) Right c) Left d) Main Flat e) Opposite Main Flat           | 90     |

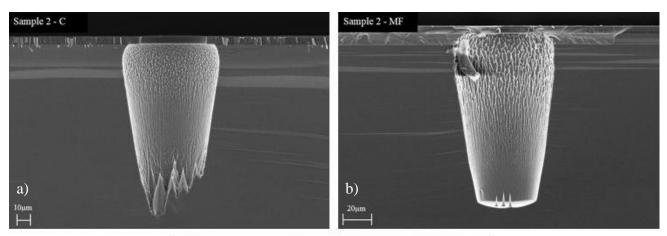

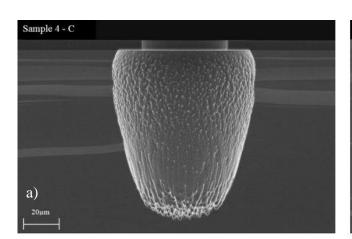

|    | Figure 37: Run 2 Results – a) Centre b) Main Flat c) Opposite Main Flat                            | 91     |

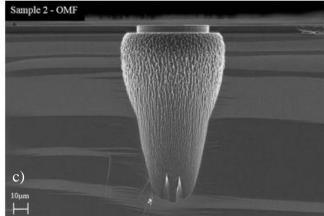

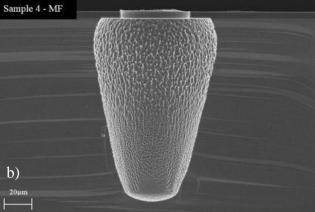

|    | Figure 38: Run 3 Results – a) Centre b) Main Flat c) Opposite Main Flat                            | 92     |

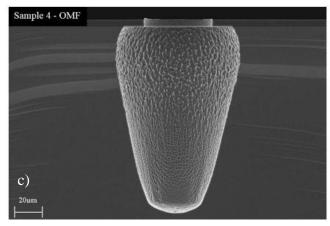

|    | Figure 39: Run 4 Results – a) Centre b) Main Flat c) Opposite Main Flat                            | 93     |

|    | Figure 40: Run 5 Results – a) Centre b) Main Flat c) Opposite Main Flat                            | 94     |

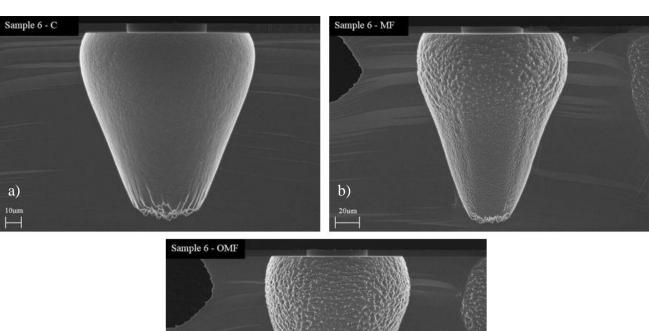

|    | Figure 41: Run 6 Results – a) Centre b) Main Flat c) Opposite Main Flat                            | 95     |

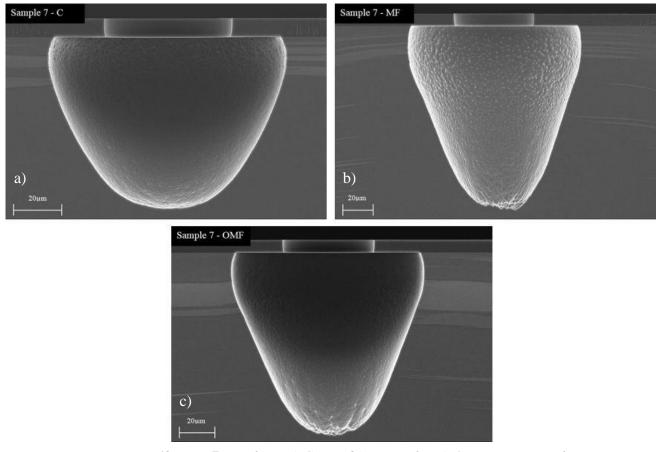

|    | Figure 42: Run 7 Results – a) Centre b) Main Flat c) Opposite Main Flat                            | 96     |

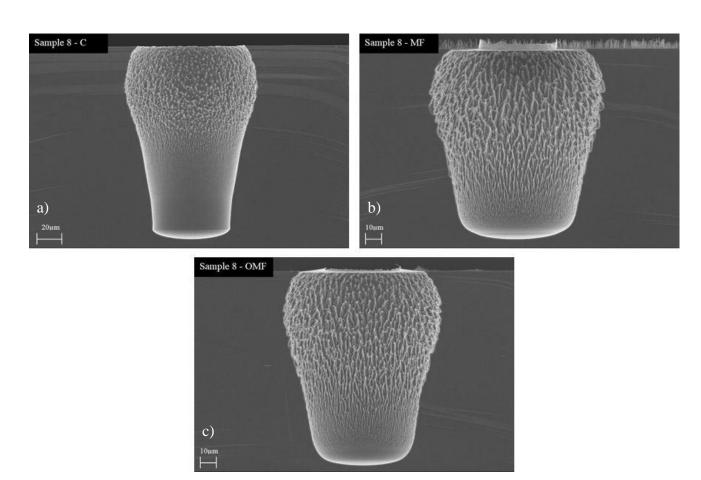

|    | Figure 43: Run 8 Results – a) Centre b) Main Flat c) Opposite Main Flat                            | 97     |

| Figure 44: Run 9 Results – a) Centre b) Main Flat c) Opposite Main Flat  | 98  |

|--------------------------------------------------------------------------|-----|

| Figure 45: Run 10 Results – a) Centre b) Main Flat c) Opposite Main Flat | 99  |

| Figure 46: Run 11 Results – a) Centre b) Main Flat c) Opposite Main Flat | 100 |

| Figure 47: Run 12 Results – a) Centre b) Main Flat c) Opposite Main Flat | 101 |

| Figure 48: Run 13 Results – a) Centre b) Main Flat c) Opposite Main Flat | 102 |

| Figure 49: Run 14 Results – a) Centre b) Main Flat c) Opposite Main Flat | 103 |

| Figure 50: Run 15 Results – a) Centre b) Main Flat c) Opposite Main Flat | 104 |

| Figure 51: Run 16 Results – a) Centre b) Main Flat c) Opposite Main Flat | 105 |

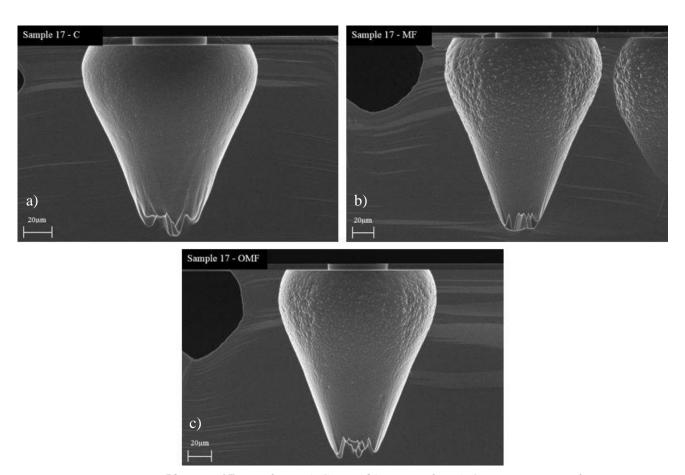

| Figure 52: Run 17 Results – a) Centre b) Main Flat c) Opposite Main Flat | 106 |

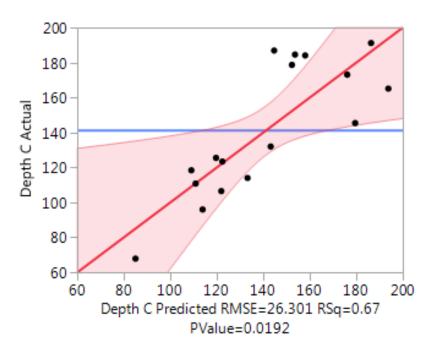

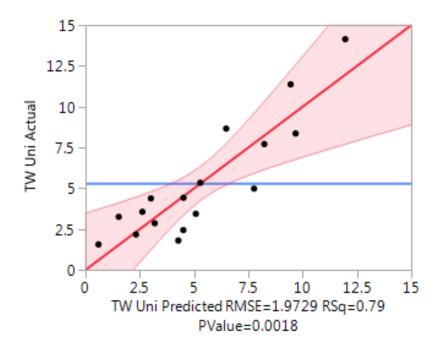

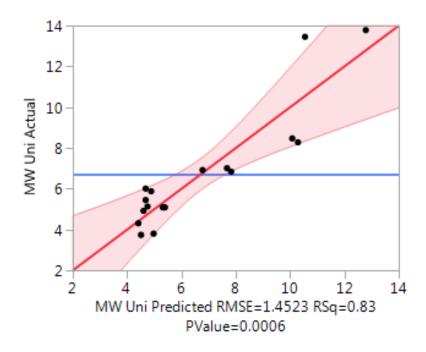

| Figure 53: Depth (C) Model Response                                      | 108 |

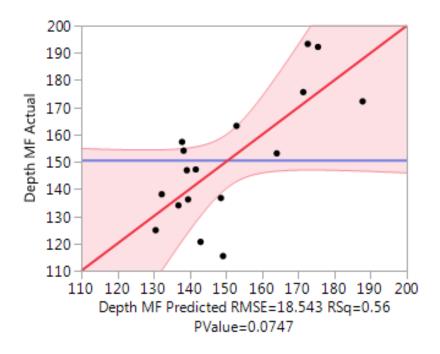

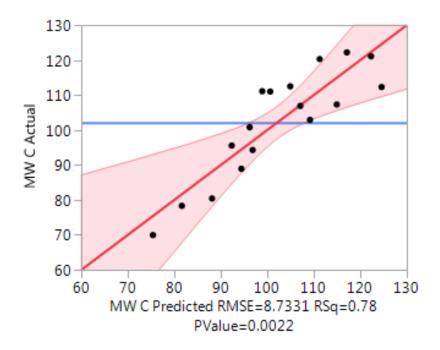

| Figure 54: Depth (MF) Model Response                                     | 109 |

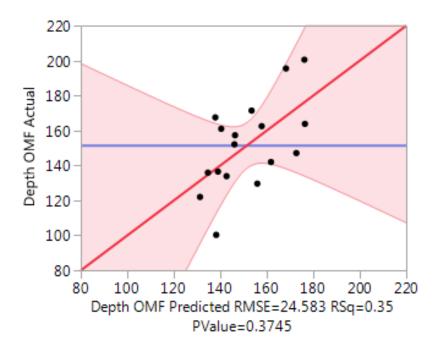

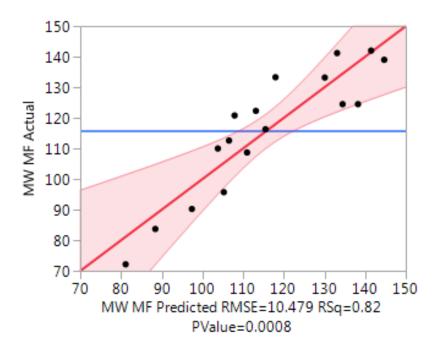

| Figure 55: Depth (OMF) Model Response                                    | 110 |

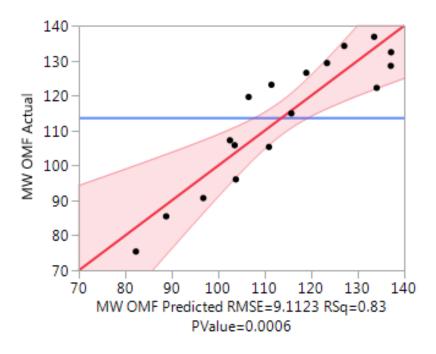

| Figure 56: Depth (Uni) Model Response                                    | 111 |

| Figure 57: Top Width (C) Model Response                                  | 112 |

| Figure 58: Top Width (MF) Model Response                                 | 113 |

| Figure 59: Top Width (OMF) Model Response                                | 114 |

| Figure 60: Top Width (Uni) Model Response                                | 115 |

| Figure 61: Max Width (C) Model Response                                  | 116 |

| Figure 62: Max Width (MF) Model Response                                 | 117 |

| Figure 63: Max Width (OMF) Model Response                                | 118 |

| Figure 64: Maximum Width (Uni) Model Response                            | 119 |

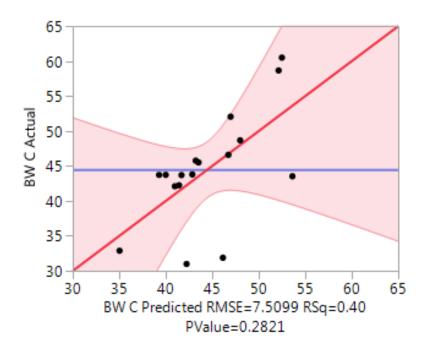

| Figure 65: Bottom Width (C) Model Response                               | 120 |

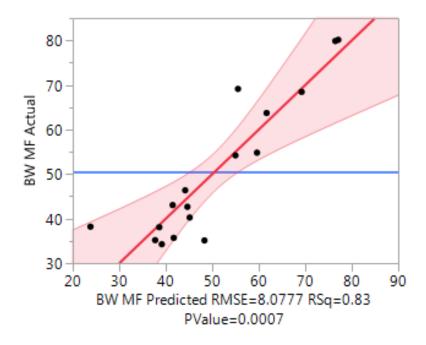

| Figure 66: Bottom Width (MF) Model Response                              | 121 |

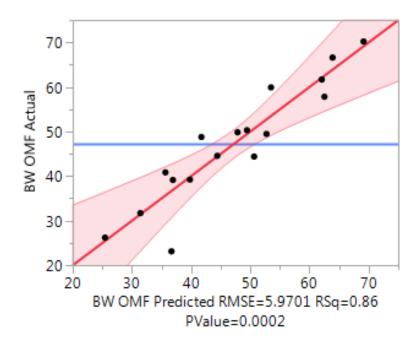

| Figure 67: Bottom Width (OMF) Model Response                             | 122 |

| Figure 68: Bottom Width (Uni) Model Response                             | 123 |

| Figure 69: Prediction Profiler                                                            | .124 |

|-------------------------------------------------------------------------------------------|------|

| Figure 70: Substrate Platform Cooling Circuit                                             | .128 |

| Figure 71: Simulation Temperature Distribution Results                                    | .130 |

| Figure 72: Simulated Results of HBC Conductivity Changes                                  | .130 |

| Figure 73: Cooling Channel Performance Simulation                                         | .131 |

| Figure 74: Esc Cooling Channel Illustration (copied with permission of SPTS Technologies) | .132 |

| Figure 75: Temperature vs across wafer non-uniformity                                     | .137 |

| Figure 76: Most Significant Parameter Summary                                             | .138 |

| Figure 77: An SPTS Rapier System® (copied with permission of SPTS Technologies)           | .140 |

| Figure 78: TSV Deposition Layer Coverage                                                  | .146 |

| Figure 79 TSV Process Profile Cross Section                                               | .146 |

| Figure 80 TSV Profile Definition                                                          | .148 |

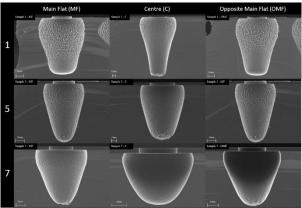

| Figure 81 Sample Results (best (5) and worst (7) case                                     | .148 |

| Figure 82 Temperature vs across wafer non-uniformity                                      | .149 |

|                                                                                           |      |

# **List of Tables**

| Table 1: Levels of integrated circuit [5]                                            | 20  |

|--------------------------------------------------------------------------------------|-----|

| Table 2: Average price of IC's and proportion of production consumed by military [9] | 21  |

| Table 3: Photo Resist Characteristics [40]                                           | 40  |

| Table 4: SF <sub>6</sub> Dissociation mechanism                                      | 50  |

| Table 5: O <sub>2</sub> Clean Parameters                                             | 69  |

| Table 6: Conditioning Run Parameters                                                 | 70  |

| Table 7: TSV Process Parameters                                                      | 71  |

| Table 8: Etch Process Trends (reproduced with permission from SPTS)                  | 76  |

| Table 9: Example L4 (2^3) Taguchi Orthogonal Array                                   | 77  |

| Table 10: DOE Run Table                                                              | 79  |

| Table 11: Process Gas Flows as a Percentage of Total Flow                            | 79  |

| Table 12: Full Results                                                               | 85  |

| Table 13: Sample mask thickness, HeLur, Selectivity                                  | 89  |

| Table 14: Run 1 Results                                                              | 90  |

| Table 15: Run 2 Results                                                              | 91  |

| Table 16: Run 3 Results                                                              | 92  |

| Table 17: Run 4 Results                                                              | 93  |

| Table 18: Run 5 Results                                                              | 94  |

| Table 19: Run 6 Results                                                              | 95  |

| Table 20: Run 7 Results                                                              | 96  |

| Table 21: Run 8 Results                                                              | 97  |

| Table 22: Run 9 Results                                                              | 98  |

| Table 23: Run 10 Results                                                             | 99  |

| Table 24: Run 11 Results                                                             | 100 |

| Table 25: Run 12 Results                                | 101 |

|---------------------------------------------------------|-----|

| Table 26: Run 13 Results                                | 102 |

| Table 27: Run 14 Results                                | 103 |

| Table 28: Run 15 Results                                | 104 |

| Table 29: Run 16 Results                                | 105 |

| Table 30: Run 17 Results                                | 106 |

| Table 31: Depth (C) Sorted Parameter Estimate           | 108 |

| Table 32: Depth (MF) Sorted Parameter Estimate          | 109 |

| Table 33: Depth (OMF) Sorted Parameter Estimate         | 110 |

| Table 34: Depth (Uni) Sorted Parameter Estimate         | 111 |

| Table 35: Top Width (C) Sorted Parameter Estimate       | 112 |

| Table 36: Top Width (MF) Sorted Parameter Estimate      | 113 |

| Table 37: Top Width (OMF) Sorted Parameter Estimate     | 114 |

| Table 38: Top Width (Uni) Sorted Parameter Estimate     | 115 |

| Table 39: Max Width (C) Sorted Parameter Estimate       | 116 |

| Table 40: Max Width (MF) Sorted Parameter Estimate      | 117 |

| Table 41: Max Width (OMF) Sorted Parameter Estimate     | 118 |

| Table 42: Maximum Width (Uni) Sorted Parameter Estimate | 119 |

| Table 43: Bottom Width (C) Sorted Parameter Estimate    | 120 |

| Table 44: Bottom Width (MF) Sorted Parameter Estimate   | 121 |

| Table 45: Bottom Width (OMF) Sorted Parameter Estimate  | 122 |

| Table 46: Bottom Width (Uni) Sorted Parameter Estimate  | 123 |

| Table 47: Comsol Simulation Values                      | 129 |

| Table 48: Statistically Significant Results             | 135 |

| Table 49 TSV Process Parameters                         | 147 |

| Table 50 DoE Run Parameters                        | 147 |

|----------------------------------------------------|-----|

| Table 51 Process Gas Flow Values                   | 147 |

| Table 52 (Figure 81) Run Result Dimensions         | 148 |

| Table 53 Statistically Significant Process Effects | 149 |

### **Definitions or Abbreviations**

IC Integrated Circuit

TSV Through Silicon Via

ITRS International Technology Roadmap for Semiconductors

ISSCC International Solid-State Circuits Conference

DRAM Dynamic random-access memory

FEOL Front End of Line

BEOL Back end of Line

CVD Chemical Vapour Deposition

PVD Physical Vapour Deposition

ECD Electro Copper Deposition

CPU Central Processing Unit

RAM Random Access Memory

DoE Design of Experiment

SEM Scanning Electron Microscope

TE Thermionic Emission

ICP Inductively Coupled Plasma

RF Radio Frequency

HeLuR Helium Leak-up Rate

FCC Federal Communications Commission

ISM Industrial, Scientific and Medical

Pegasus Plasma Etch Giving Advanced Speed Uniformity and Selectivity

RSq R Square

RMSE Root Mean Square Error

ESC Electrostatic Chuck

W/mK Watts per meter-kelvin

Torr A unit of pressure equivalent to 1mm of mercury in a barometer

## **Chapter Content Descriptions**

The contents of this programme of work are as follows: -

- Chapter 1 describes the history behind the integrated circuit from the time of its invention to current levels of technology and follows on to explain the evolution of the through silicon via and its manufacturing limitations.

- Chapter 2 introduces the design of experiments criteria and the analytical techniques that are used to investigate the manipulation of the positive profile TSV.

- Chapter 3 details the results obtained from the DoE etch process runs and explains the outcome from the data regression analysis.

- Chapter 4 discusses the steps taken with computer modelling simulation to eliminate the

possibility that the across wafer non-uniformity changes were being affected by the wafer

platform temperature.

- Chapter 5 explains the conclusions that were drawn from this programme of work and identifies areas that will allow the research to be expanded.

- Chapter 6 introduces the research paper that resulted from this program of work that was

presented to the IMAPS 16th International Conference and Exhibition on Device

Packaging.

## Chapter 1 - Introduction

This chapter details the history of the integrated circuit from the time of its invention to current technology levels, following on to explain the evolution of integrated circuits and details why the through silicon via (TSV) was developed. The discussion then turns to some of the process and manufacturing limitations associated with the production of TSV's and how they are typically overcome, finishing with an investigation into current research on positive profile TSV manipulation and the expected scope of this programme of work.

### 1.1 Integrated Circuit History

The integrated circuit (IC) is sometimes referred to as a silicon chip or microchip and is a piece of silicon about the size of a small fingernail on which interconnected transistors, capacitors and resistors are fabricated as a single assembly. The IC is ubiquitous in everyday life and is used in virtually every piece of modern technology from washing machines to televisions, computer games consoles, military aircraft, or the International Space Station, all will have many integrated circuits embedded within them to control their operation.

The transistor is a semiconductor device which is a fundamental building block for all modern electronic devices, it consists of three layers of semiconductor material that are sandwiched together. When a current or voltage is applied to the centre layer of the stack it produces a large change in the current passing between the two outer layers, it is this effect that allows the transistor to be used as a switch or an amplifier in an electronic circuit. A working model of the junction transistor was first demonstrated by William Shockley and his team at Bell Laboratories in New Jersey USA in December 1947 [1]. In the years after its invention computer engineers used the transistor to increase the performance of their designs. Computers were initially constructed from a series of discrete components with each module performing a single task, however each unit needed to be physically wired and soldered to every other component in the system by hand, this meant that even a single incorrectly soldered joint could make the whole computer fail to operate. As computers became more powerful the performance enhancements were tied to the increasing complexity of the designs, this added ever growing numbers of interconnects between components inside the computer which resulted in the new models becoming increasingly unreliable as additional modules were added.

This problem was described by J. A. Morton, Vice President of Bell Laboratories in his June 1958 article "The Technological Impact of Transistors" at the "Proceedings of the IRE" (Institute of Radio Engineers) celebrating the 10 year anniversary of the invention of the transistor in which he described the "Tyranny of Numbers" [2]

"Such systems, because of their complex digital nature, require hundreds, thousands, and sometimes tens of thousands of electron devices. The large amount of power used inefficiently and the high cost of reliability of the electron tube have prevented these expansions of electronics in all but a few cases where the high cost could be tolerated, even though not desired"

Jack Morton – Bell Laboratories

Two months after Jack Morton made this speech, on the 12<sup>th</sup> September 1958, Jack Kilby of Texas Instruments managed to demonstrate the first working integrated circuit by manufacturing resistors and capacitors from a single piece of germanium and then wiring them into a transistor circuit [3]. Six months later, Robert Noyce of Fairchild Semiconductor invented a way to interconnect the capacitors, resistors, diodes and transistors of a circuit by laying a metal film over the semiconductor material and etching away the unnecessary parts to create the connections between each component [4], it was these two advances in technology that greatly reduced the size of computer components by removing all of the manual interconnects between each component, and allowed them to be mass produced.

There are 5 levels or generations of integrated circuit which are shown in Table 1.

Table 1: Levels of integrated circuit [5]

| Level | Title                                | Active devices per<br>chip |

|-------|--------------------------------------|----------------------------|

| 1     | Small Scale Integration (SSI)        | < 100                      |

| 2     | Medium Scale Integration (MSI)       | 100 – 10,000               |

| 3     | Large Scale Integration (LSI)        | 10,000 – 100,000           |

| 4     | Very Large-Scale Integration (VLSI)  | 100,000 to 1 million       |

| 5     | Ultra-Large-Scale Integration (ULSI) | > 1 million                |

Small scale integration (SSI) circuits were essential for early aerospace projects and they were extensively used for the guidance systems in the Minuteman II & III nuclear weapons systems [6] and the Apollo Moon Programme [7]. The main advantages of the IC over discrete electronics in these applications were a decrease in the size, weight and power consumption against comparable components which are features that are crucial in a system where every extra gram of weight increases fuel consumption [8]. In the years between 1962 and 1964 the United States Government purchased nearly all the supplies of integrated circuits that were available as can be seen in table 2. It was this guaranteed market provided by the US Government that allowed the IC manufacturers to invest and expand the device production when costs were high and yields were low, this supported the fledgling market until the IC manufacturing costs dropped to a point at which they became attractive for commercial uses [9].

Table 2: Average price of IC's and proportion of production consumed by military [9]

| Year | Average Price (\$) | Consumed<br>by Military<br>% |

|------|--------------------|------------------------------|

| 1962 | 50 – 100           | 100                          |

| 1963 | 31 – 60            | 94                           |

| 1964 | 18 – 50            | 85                           |

| 1965 | 8 – 33             | 72                           |

| 1966 | 5 - 33             | 53                           |

| 1967 | 3 – 33             | 43                           |

| 1968 | 2 - 33             | 37                           |

The ceaseless drive to put an ever-increasing number of circuit functions on a chip has provided the incentives to keep scaling down the devices in size. As the number of devices per IC are increased you achieve the additional benefits of higher yields, improved reliability, lower manufacturing costs and increased performance [10]. It was Gordon Moore in 1965 who first tabled the idea that device transistor density approximately doubles every year [11], but he revised this figure to doubling every two years in 1975. This rule which in now known as Moore's Law has held true since 1975 and is used to guide long term plans and research targets for the Semiconductor industry. While no specific limit has been established, it appeared that the validity of Moore's law for consumer electronics would cease at critical dimensions (CD's) smaller than  $0.05\mu m$  (5 nanometres) due to fundamental limiting factors stemming from electron thermal energy and quantum mechanical tunnelling [12] through the gate oxide layer [13].

### 1.2 2.5 D and Beyond

Transistor miniaturisation was still the main focus of the semiconductor industry as recently as 2013, when the penultimate International Technology Roadmap for Semiconductors (ITRS) was released [14]. The report concluded that the physical gate length (an indication of how far current must travel within the device) of the transistors was predicted to shrink until at least 2028. The semiconductor manufacturers when being faced with ever increasing development and production costs to keep up with the pace of Moore's law decided that that the future led in a direction away from continual shrinking of transistor dimensions [15]. The path investigated was to build circuits using three dimensional concepts rather than the historical two-dimensional chips. The idea of building devices in three dimensions is not a new concept, with this being first identified by J. M. Early of Bell Labs who proposed the stacking of a number of components in a cubic configuration at the ISSCC (International Solid-State Circuits Conference) in February 1960 [16]. But it was not until ~2010 when the technology to manufacture these devices became cost effective, with the Intel "Ivy Bridge" CPU products becoming the first commercial 3D devices to be introduced to market in April 2012 [17]. The final ITRS 2.0 report released in April 2016 embraces the trends toward 3D architecture and predicts an end to the traditional shrinking of chip features by the early 2020's as it will become more cost effective to produce 3D IC's. Paolo Gargini the chair of ITRS said that the idea that we are facing an end to Moore's Law is completely wrong, stating that there is only one way of defining Moore's Law and that is that the "number of transistors doubles every two years." The law is simply a prediction on how many transistors can fit into a given area of IC irrespective of the whether it's done in a single layer or the stacking of multiple layers [15].

### 1.3 Integrated Circuit Packaging Types

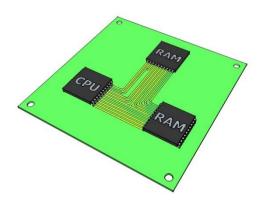

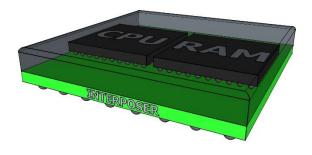

Figure's 1 to 3 show the evolution of the integrated circuit layout since its invention in the early 1950's.

Figure 1: Traditional CPU/RAM

Figure 1 shows the typical circuit layout that is easily recognisable, where each device is separate on a circuit board and is connected via conductive 'tracks' running along the surface of the non-conductive substrate.

Figure 2: CPU/RAM in a single package (2.5D)

Figure 2 indicates the typical construction of a 2.5D assembly where individual devices are placed close together, and the connections are made via 'through silicon vias' (TSVs) and tracks inside the interposer layer which is used to spread the connections between the individual devices, this assembly is usually packaged together as a unit and has external connection points to allow for insertion into a larger assembly [18].

Figure 3: True 3D IC Package

Figure 3 shows a full 3D assembly, this is a device that has 2 or more layers of active components that are integrated both horizontally and vertically into a single package. All components in the layers communicate using on-chip signalling which minimises the internal signal connection lengths allowing for faster operation, less heat production and lower power consumption [19].

#### 1.4 Through Silicon Vias (TSVs)

The key enabling technology for 2.5D and 3D IC packaging solutions is the through silicon via, the TSV is a conductive plug (usually formed from one of three materials, copper, tungsten, or polysilicon (poly-Si) which passes completely through the silicon die and forms connection points on the top and bottom surfaces of each layer. These connection locations allow additional component layers to be easily added allowing three dimensional integrated circuits to be constructed [18]. Figure 4 shows a cross section through a Samsung DDR4 Dynamic random-access memory (DRAM) memory device that displays a practical example of a TSV, the plug locations and the soldered connections between the individual DRAM dies are clearly visible in the 'underfill' sections indicated on the image.

Figure 4: Samsung DDR4 DRAM Memory Stack (Source: Samsung 3D TSV, Stacked DDR4 DRAM report – System Plus Consulting, 2015.)

#### 1.5 TSV Construction

TSVs can be fabricated at three positions in the device assembly process with each type of TSV having specific roles. TSV diameters are typically in the range of 0.2µm-100µm depending on the feature application, although it should be noted that as the diameter of the TSV reduces, the substrate thickness and TSV depth must also lower to preserve the aspect ratio of the feature below 20:1. This is to ensure that the etch and subsequent material fill can be assured to be of sufficient quality for successful manufacturing [20].

Via First – The TSV features are fabricated before any of the device components, the main drawback with this method is that the filling material is exposed to the full front end of line (FEOL) temperatures (>400°C) [21], this limits the choice of filler material to either tungsten (W) or poly-Si, as copper (Cu) will migrate into the surrounding material at these temperatures. A key advantage with this method is that it is the simplest approach as there is no consideration needed for contamination or alignment of the TSV structures.

Via Middle – The TSV is created after the FEOL processes are complete but before the back end of line (BEOL) processes have begun, as a result the TSV is not subjected to the high temperatures that are required during the frontend process steps. A benefit of these lower heat loads is that copper can be used as the filler material as it will not migrate at lower processing temperatures. Copper is the preferred filler material due to its cost, low electrical resistance, compatibility with conventional interconnections, and is a good match to the coefficient of thermal expansion of silicon [22].

Via Last – The TSV's are created either during the formation of the Si BEOL structures, or at the end of the process when the wafer is effectively complete. The structures created at this stage in the process see very little heat load (<160°C) and the process steps are considered to be low temperature [23], it has the disadvantage that the alignment of the TSV's to the die needs to be accurately positioned so that none of the completed components are damaged [24].

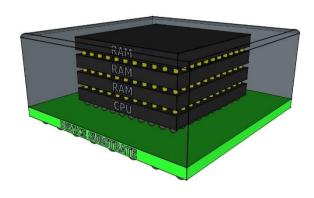

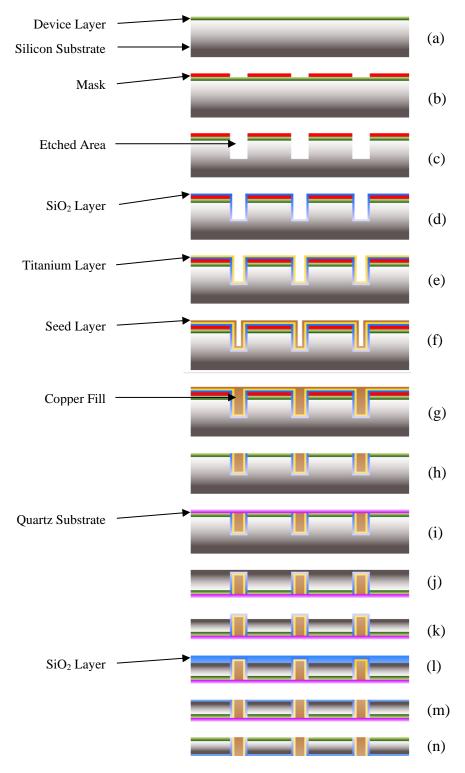

Figure 5: Typical TSV (via middle) Manufacturing Process

The list below explains the process steps that are illustrated in Figure 5, this a typical production method for a TSV irrespective of where in the process flow it is constructed.

- (a) A substrate with the required device layer is prepared to the requirements of the application.

- (b) A mask with the desired feature pattern is formed upon the surface of the substrate using a photolithographic process.

- (c) The wafer is placed into an etch chamber and the features are etched to the required depth.

- (d) A silicon oxide (SiO<sub>2</sub>) layer is deposited via CVD (Chemical Vapour Deposition) onto the surface of the substrate, this is a dielectric material and acts as an insulating layer to prevent electrical contact between the copper plug and the silicon substrate.

- (e) A titanium (Ti) layer is deposited via PVD (Physical Vapour Deposition) onto the surface of the substrate which acts as an adhesion layer allowing the copper plug to adhere firmly into the assembly.

- (f) A copper seed layer is deposited onto the Ti layer via PVD and is used to prevent voids forming inside the copper plug during its formation.

- (g) Copper is deposited onto the surface of the seed layer, covering the entire surface of the substrate whilst filling in the etched plug holes. The filling process can be performed using PVD, but more commonly it is laid down using an electro copper deposition (ECD) process.

- (h) The entire stack of layers is ground or etched back to the device layer which leaves isolated vias within the device layer.

- (i) A quartz substrate is bonded to the top of the device layer.

- (i) The stack is flipped over so that the quartz becomes the base layer.

- (k) The silicon substrate is etched away to expose the SiO<sub>2</sub> covered copper plugs.

- (l) A further SiO<sub>2</sub> layer is deposited via CVD onto the entire surface of the substrate to a sufficient depth to cover the proud standing copper plugs.

- (m)The SiO<sub>2</sub> is exposed to either etching or a grinding process that removes the excess material exposing the surface of the copper plug.

- (n) The assembly is flipped over, and the quartz substrate is removed.

The completed assembly has a device layer with external connection points on both the top and bottom surfaces, these connection points will allow other components and modules to be intimately connected to the device in order to construct close coupled three dimensional structures [24].

#### 1.6 TSV Profile Undercut Formation

This programme of work specifically deals with positive etch profiles and anomalies related to the manufacture of these features. This project will focus on the positive etch profile as opposed to straight or negative profiles [25] since the positive profile is the most widely used shape for TSV manufacturing as it has been proven to be more cost effective overall to produce than the other profile shapes.

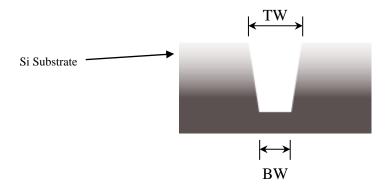

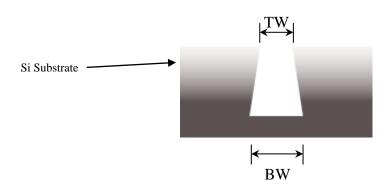

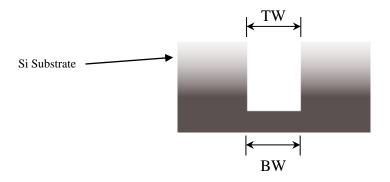

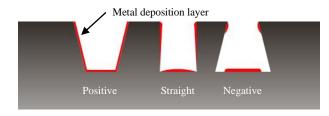

Figure 6: TSV Feature Profiles [25]

This cost benefit is provided by the ease of producing follow on manufacturing steps that involve either metal or insulating material deposition; a positive profile with a smooth sidewall will produce the most consistent results for follow on manufacturing processes as no part of its shape overhangs any other part of the structure. A negative profile has a bottom width that is larger than its top width, and as a result a large part of the feature will be shadowed by the top opening of the profile. The straight profile has vertical 'cliff edges' which can cause difficulties obtaining a consistent film thickness and deposited material will naturally gravitate towards the bottom of the feature causing inconsistent film thicknesses [26].

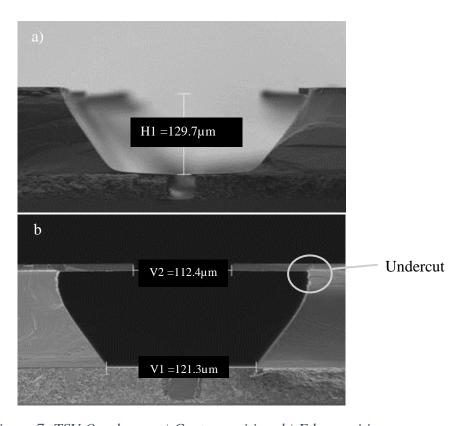

One of the largest defects resulting from the positive etch process is the formation of a feature at the top of the profile that is often known as an 'overhang', 'undercut' or 'lateral etching'; where the area directly below the mask is narrower than the widest dimension of the TSV structure as shown in Figure 7b. There are two main factors that influence its formation with the minor effect being the SF<sub>6</sub>:O<sub>2</sub> ratio which can reduce the size of the undercut, but has the added effect of adjusting the taper angle of the holes as the ratio is changed [27]. For this series of experiments the SF<sub>6</sub>:O<sub>2</sub> ratio has been fixed at 1.95:1 for the duration of this design of experiments (DoE) to minimise a known effect on the TSV profile shape skewing the interpretation of the results. The major effect that influences the size of the undercut is 'ion scattering' where the fluorine (F) ions are deflected by the edge of the mask into the top area of the feature and has the effect of significantly increasing the lateral etching in this area leading to the formation of the undercut, the level of lateral etching appears to be dependent on time/etched depth rather than depth/width (aspect ratio) [28]. Figure 7 (a) shows a positive profile TSV structure with no undercut at the top of the feature, Figure 7 (b) displays the same structure at a different location on the substrate which clearly shows the undercut formation.

Figure 7: TSV Overhang, a) Centre position, b) Edge position

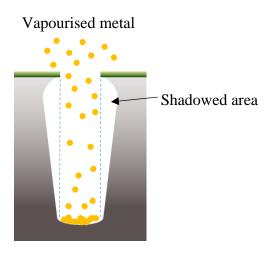

The next step in the manufacturing procedure after the TSV profile has been etched is to add a layer of metal via a physical vapour deposition (PVD) process, the film created by the PVD process is plasma vapourised from a metal target located at the top of the process chamber onto the wafer by gravity with no form of additional attraction. For this metallic film to be evenly distributed over the surface of the profile there must be a clear line of sight to all parts of the feature from the opening at the top of the TSV, no part of the internal surface of the structure must be overhanging any other part of the structure as documented in the introduction.

The presence of an overhang means that the top of the structure is covering at least some of the area below it, this creates a shadowed area that cannot be coated by the deposited metal layer as shown in [29], the overhang feature can be clearly seen in the SEM photograph of every process run that is detailed in the results section.

Figure 8: Overhang Shadowing Effect

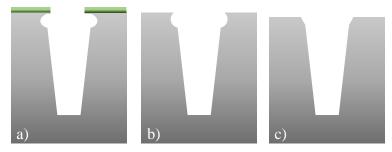

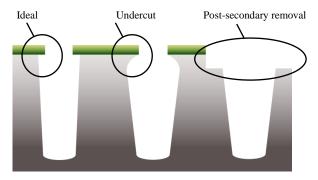

### 1.7 Two Stage Undercut Removal Method

When a semiconductor device requires a TSV it is usually because this device is part of a larger assembly that will have other components connected to it. The size and position of the TSV's are crucial and are required to be consistent across the entire wafer surface to ensure that any mating parts line up accurately in further process steps as can be seen in Figure 4. The presence of an undercut is not ideal, as its size and uniformity at various locations across the wafer may not be consistent as shown in Figure 7 (a) & (b), with the resulting negative profile at the top of the TSV making it difficult to successfully deposit continuous insulating, diffusion and seed layers by standard deposition processes as the bowed surfaces are likely to create voids during the trench filling steps [29, 30]. Consequently, a follow on 'thinning' process is required to remove the undercut, leaving the feature with no overhanging areas. The removal of the undercut leaves a much more controllable feature as the sidewalls below the lateral etching region are more likely to conform to the feature dimension requirements due to a lack of lateral etching effects. A typical thinning process flow is shown in Figure 9, and typically follows these three steps irrespective of the method used to thin the material.

- 9 (a) Completed etch process

- 9 (b) Mask removal

- 9 (c) Thinning process

Figure 9: Typical overhang process flow removal process [31]

The 'thinning' procedure is another production process that involves physically stripping away the top layer of the substrate to a depth slightly below the bottom of the lateral etching region. This can be done by either a plasma etch blanket removal process where the top surface of the substrate is etched away in an ICP reactor [31], or by physically grinding the surface of the substrate away using a semiconductor grinding machine [32]. Whilst either thinning method can adequately remove the excess material, grinding can remove material at a faster rate than dry etching, but the final wafer thickness is more difficult to control. Testing has shown that grinding causes a damaged layer roughly 200nm thick that has large compressive stress leading to a concavely bowed substrate that requires an additional stress relief process when the griding is complete [33]. Dry etching is a slower method of material removal but it typically has an improved surface roughness value and chip strength is up to 50% greater after the process is completed, as stress is not introduced into the substrate during thinning, there is no requirement for a stress relief step at the end of the process [34].

The fact that the process is necessary adds additional costs and time to the production of the devices that could be avoided if the correct process recipe parameters are identified that create the TSV with the required profile during the etch step.

### 1.8 Current Research on Undercut Manipulation

Recent research shows that the size of the undercut or 'local bowing' as it's sometimes described is dependent on the depth of the trench. As the etch progresses the TSV profile becomes deeper and larger with the undercut formation following this trend, the scope of the research so far is limited to parallel profile trenches and not the positive profiles that are being discussed in this project. Researchers [30] additionally found that the undercut form seemed to be dependent on the balance between the relative ion density and the fluorine/oxygen gas ratio, it was theorised that by adjusting the gas ratio you could alter the balance between passivation and sidewall etching. The ion density appeared to be key in the size of the undercut, as increasing the RF energy causes the undercut to increase in size. The researchers concluded that increasing the RF energy leads to more ion production but an unanswered question remained as to the mechanism behind the obvious pathway deviation of the ions away from the normal vertical direction of travel [30].

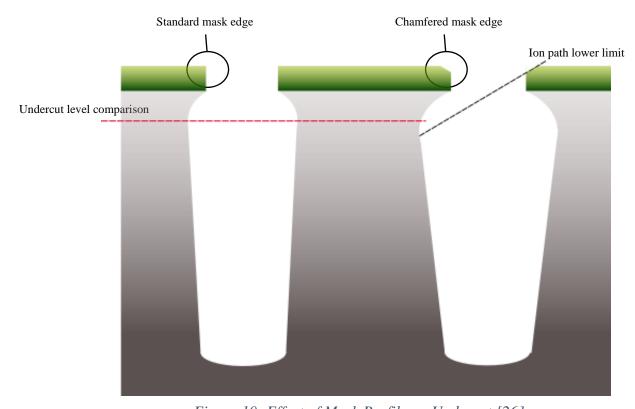

In a follow up study to this research, a separate team took the conclusion from the research paper written by M. Boufnichel and attempted to answer the question of why the ions appeared to be deviating from their vertical path and hitting the sidewalls of the feature, thus assisting in the formation of the undercut. The research was initiated by adjusting the ratio between the O<sub>2</sub> and SF<sub>6</sub> process gasses and it was observed that by changing this ratio the amount of lateral etching can be greatly reduced, but it was also found that adjusting this ratio produced strongly tapered sidewalls which is the effect that will be exploited in this programme of work. The researchers used a Monte Carlo simulation [35] to predict the transportation of etch species into the features and measured the numbers of fluorine radicals interacting with the sidewalls, the results of this test showed that the F radicals have a large effect on the etching of the sidewalls at the top of the feature, but this effect reduces with depth. It was concluded that this mechanism is responsible for the tapered sidewalls but cannot fully explain the type of lateral etching formation that appears during the etch process. It was noted during the experiments that the corner of the mask was becoming etched, and a chamfer was forming; if a line

was drawn down the chamfer angle and continued until the line intersected the feature sidewall it corresponded with the bottom of the lateral etching region. To prove this effect researchers have deliberately created a chamfered feature at the mask hole edge and ran the same etch process on the sample. It was recorded that the angle of the chamfer always predicted the bottom of the lateral etching region, increasing the etch time for these runs also increased the size and depth of the lateral etch feature. As a direct result of these trials the researchers concluded that the major mechanism in the formation of the undercut was ion scattering from the edge of the mask, the magnitude of the lateral etching effect was not influenced by mask thickness or material. The effect of the two mask edge profiles is illustrated in Figure 10, the black line shows that the lowest extent of the undercut region corresponds with the angle of the mask profile. The red line indicates that the lower regions of the lateral etching is less formed in a mask with a standard edge when all other process parameters are equal [28].

Figure 10: Effect of Mask Profile on Undercut [26]

# 1.9 Scope of the Research

This programme of research was designed to investigate the relationship between the specific process parameters that are deemed to be the most important factors when creating a positive profile through silicon via, the shape and the across wafer uniformity of the resulting etched features. The scope of the test is limited to the effect that the parameters have on each of the feature variables that are identified as part of the programme, the creation of an 'ideal' shape will not be investigated as part of this design of experiments.

# Chapter 2 - Methodology

Chapter 2 describes the objectives that this thesis will achieve, the decisions and technology that were required for this research program to progress and covers the hardware and reactor process conditions needed to manufacture a positive profile TSV. In the latter areas of this section, the design of experiments (DoE) conditions and parameters are discussed along with the methods for categorising and analysing the results that would be obtained from the process trials.

# 2.1 Objectives of the Research

The objective of this research programme was to determine if the shape and across wafer non-uniformity of a positive profile TSV can be manipulated by adjusting the etch process parameters that are used to create these features. These TSV profiles are a relatively new technology with Intel 'Ivy Bridge' CPU being the first major product using these devices brought to market in 2012 [17]. Due to the short period of time since their introduction the manufacturing process used to construct the assemblies has not yet matured to the point where the excess costs have been removed [36].

This project attempted to identify the critical parameters than can be used to adjust the profile of the device that would allow subsequent processing steps to be fine-tuned for faster, more consistent results, which should in turn lower cost of production per die. Once costs lower to the point where high volume production suppliers can enter the marketplace with lower initial setup costs, the availability of the devices will be increased allowing for the devices to be installed into new applications [37].

The process used to research the TSV profile dimensions was to run an experimental series of 17 SPTS type-AT test wafers through an SPTS Pegasus<sup>TM</sup> deep silicon etching system. The first wafer (run 1) was baseline processed using the conditions detailed in Table 7, the remaining 16 wafers were individually run with the modified process conditions detailed in Table 10 (runs 2-17). Each wafer was cleaved using the process detailed in section 2.15 and the resulting samples were measured and photographed using a Carl Zeiss Sigma HV scanning electron microscope (SEM).

When all the results from the process samples were collated, the resulting information was analysed using JMP Statistical Discovery™ regression analysis software. This software will compare all results against each process parameter change and will attempt to identify any predicable patterns. The results of the regression analysis were investigated for any likely etch parameter changes that would allow the researcher to intentionally affect the TSV profile dimension sizes and across wafer non-uniformity.

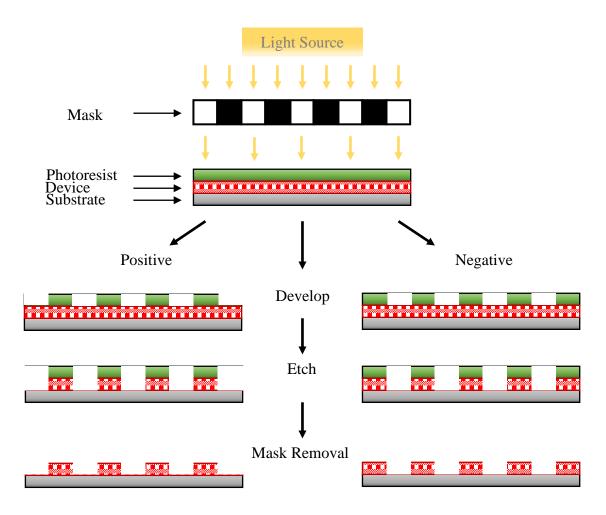

# 2.2 Photolithography

Optical (photo) lithography is a photographic process which is commonly used in the fabrication of integrated circuits to facilitate the preferential etching of features in the surface of the substrate [38]. This process step is achieved by shining a light or another form of exposing radiation such as UV or X-rays through a plate known as a photomask onto a light sensitive polymer called a photoresist.

The photoresist material is a polymer that is placed onto the surface of the wafer and is exposed and developed to form a 3D relief image on the substrate. The main role of the polymer is to resist etching during the process step so that the pattern defined by the mask can be transferred into the substrate surface.

The photomask (which is frequently shortened to 'mask') is an opaque plate that has transparent sections that are the negative of the desired pattern to be transferred to the substrate. The light source is placed above this mask with the wafer below it. Once the source has been activated, the light passes through the transparent sections in the mask and exposes the photoresist, this causes a chemical reaction in the areas that have been exposed to the light source and a developer material usually tetramethylammonium hydroxide (TMAH) is used to remove the exposed sections of the photoresist [39].

There are two types of photoresists which are used according to the required application, positive resist is soluble in the areas exposed to the light source, negative resist is soluble in the areas that are masked from the light source. Each type has its own benefits and drawbacks [40].

Table 3: Photo Resist Characteristics [40]

| Negative resists characteristics: -            | Positive resists characteristics: -   |

|------------------------------------------------|---------------------------------------|

| + High sensitivity to developers.              | + Excellent device resolution.        |

| + Good adhesion to the wafer.                  | + Aqueous developers can be used.     |

| + High plasma etch resistance.                 | + Minimal distortion from developers. |

| + Lower cost than positive resist.             | + Excellent plasma etch resistance.   |

| - Toxic organic developers are needed          | - Poor wafer adhesion                 |

| - Image distortion from the organic developers |                                       |

Figure 11: Photolithography Process [39]

### 2.3 Selection of substrate material and mask pattern

#### 2.3.1 Substrate Material

While there are several materials that can be used as substrates in the semiconductor industry the two most common are silicon (Si) and germanium (Ge). These were selected because they are elemental semiconductors (from group 14 of the periodic table) with diamond like orderly atomic structures and relatively strong atomic bonds, this provides the crystal with strong mechanical properties that are advantageous for mechanical handling and processing [41]. Each material has its own advantages, with germanium having more free electrons over silicon at any temperature within its operating range, and silicon which is by far the most common semiconductor material as it is inexpensive to manufacture and readily available, as it is the second most common material in the earth's crust (by weight) [42]. The native oxide of silicon, is silicon dioxide (SiO<sub>2</sub>) which is a hard etch resistant material that grows spontaneously on the surface of the wafer due to plasma oxidation [43], this property is frequently used to stabilise the surface of silicon semiconductors during process conditions. The ability to form SiO<sub>2</sub> on the surface of the wafer is the main reason for silicon to be chosen as the substrate material in this series of experiments as this effect is exploited during the process runs to limit isotropic etching of the TSV sidewalls [44].

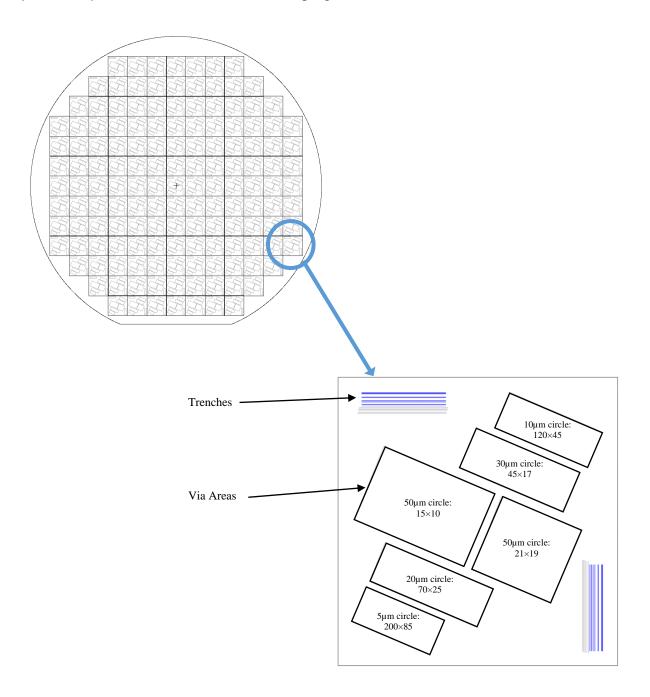

#### 2.3.2 Substrate Mask Design

The standard design of test substrates used within SPTS Technologies (SPTS) for trench and TSV etching trials are known as 'Type A' patterned wafers and are coated with a 3µm deep photoresist mask. For the purposes of this test, it was decided to use 'Type AT' wafers (see Figure 12) which have the same mask pattern as a Type A wafers, however they have an 8µm photoresist mask. This allows the etch to be run for a longer duration resulting in a greater profile depth over Type A wafers which permits a more complete formation of the undercut feature.

The mask is transferred onto the surface of the wafer resulting in 145 dies that are each a  $10\text{mm} \times 10\text{mm}$  square, the pattern has a series of holes and trenches that are detailed in Figure 12. Each die has a series of test via patterns that consist of circles  $5\mu\text{m} \times 9500$ ,  $10\mu\text{m} \times 5400$ ,  $20\mu\text{m} \times 1750$ ,  $30\mu\text{m} \times 765$  and  $50\mu\text{m} \times 549$ . The trenches in each die consist of  $3.7\mu\text{m} \times 5$  with  $1 \times 3\mu\text{m}$ ,  $5\mu\text{m}$ ,  $10\mu\text{m}$ ,  $20\mu\text{m}$ ,  $30\mu\text{m}$  and  $50\mu\text{m}$  but these are not used in this programme of work.

Figure 12: Test Wafer Layout (copied with permission of SPTS Technologies)

# 2.4 Substrate Etching

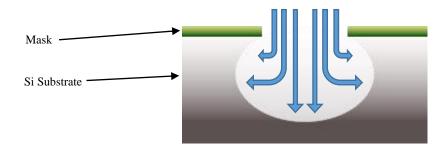

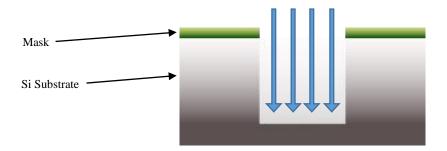

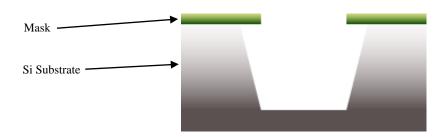

In order to generate the formation of a TSV, the substrate material needs to be subjected to a production process that preferentially etches the desired features into the surface of the substrate material. During the etch removal process there are two types of etch profile that can be produced, these are known as isotropic (a profile that is etched in all directions) and anisotropic (a profile that has selectively etched in one direction), the differences between the two are shown in Figure 13 & Figure 14 below [45].

Figure 13: Isotropic Etch Profile [45]

Figure 14: Anisotropic Etch Profile [45]

The majority of etch processes use one of the two process types detailed above, in this programme a combination of the process types will be used as the via will need to increase in width as well as depth in a controlled manner. This mix of the two forms is required to produce the characteristic tapered sidewalls of a positive etch profile [46] as shown in Figure 15.

Figure 15: Positive Etch Profile [46]

There are two main methods to etch a desired profile in a silicon substrate and these are known as either chemical wet etching or (dry) plasma etching.

# 2.4.1 Chemical Wet Etching

Chemical wet etching is a material removal process that uses liquid chemicals to remove material from the surface of the substrate and typically results in an isotropic etch profile [47]. A mask is placed onto the surface of the wafer using photolithography, this mask defines the areas that are not to be removed during the etching process and form a reverse image of the final product.

A wet etch uses liquid chemicals to consume the exposed substrate material, there are normally three steps to an etch process, these are typically: -

- 1. Diffusion of the liquid etchant into the substrate material.

- 2. The subsequent reaction between the etching materials and the material that is being targeted, this is normally a reduction/oxidation (redox) reaction.

- 3. Removal of the reactant material and etch products from the surface of the substrate.

Typical chemicals that are used for these reactions are (1) Sulphuric acid (H<sub>2</sub>SO<sub>4</sub>), Ammonium Hydroxide (NH<sub>4</sub>OH). (2) Hydrogen Peroxide (H<sub>2</sub>O<sub>2</sub>), Nitric Acid (HNO<sub>3</sub>). (3) Water (H<sub>2</sub>O), Acetic Acid (CH<sub>3</sub>COOH) [48].

#### 2.4.2 Plasma Generation

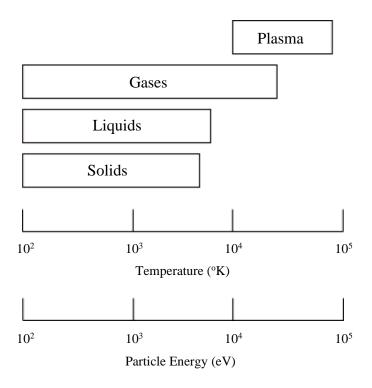

A plasma is a partially ionised gas that is energetically the fourth state of matter and contains roughly equal amounts of positively charged ions and negatively charged electrons, Figure 16 represents the ranges of temperature (particle energy) in which each of the 4 stages of matter typically occur [49].

Figure 16: Matter State Vs Temperature [49]

In a typical neutral gas no forces are present between its molecules and they travel with a range of velocities, the movement of the molecules exhibit Brownian motion where the path taken by each molecule is controlled solely by collisions amongst the fast moving atoms and molecules within the gas, and impacts on the walls of the container [50].

#### 2.4.3 Ionisation

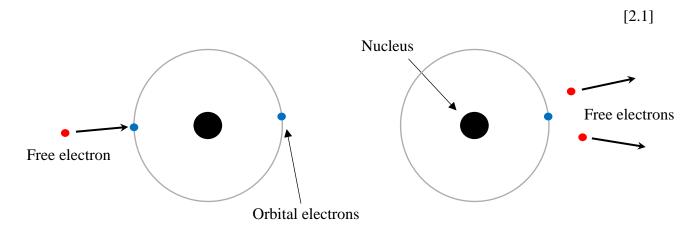

A plasma can be defined as a quasi-neutral (similar number of positive and negative charges) gas of charged and neutral particles that exhibit a collective behaviour, in order to create a plasma three important processes will take place which are known as ionisation, excitation-relaxation and dissociation [51].

Free electrons are naturally present in any gas due to natural ionisation, these electrons are accelerated using a rotating magnetic field within a vacuum chamber until enough energy is gained to knock an orbital electron away from a gas molecule creating an ion as illustrated in Figure 17 [52].

Figure 17: Ionisation of a gas molecule within a plasma reactor

The free electrons formed during the process of ionisation are continually generated and lost within the plasma by a process known as recombination, the plasma enters a stable state once the number of electrons that are lost is equal to the numbers that are being created.

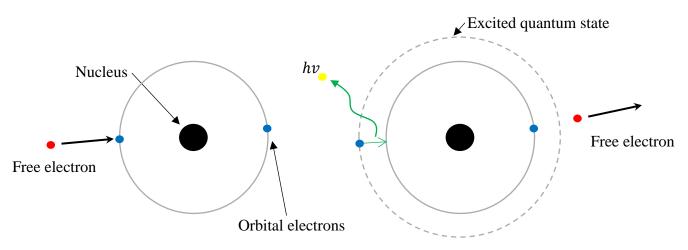

### 2.4.4 Excitation – Relaxation

When fully formed the plasma will glow with a particular colour that is directly related to the gas molecules that are present in the reactor, for example argon (Ar) will glow light purple, xenon (Xe) will glow blue, nitrogen (N<sub>2</sub>) will glow pink. The colour or 'glow discharge' is caused by an excitation-relaxation reaction and is emitted when a free electron strikes a gas molecule with insufficient energy to cause ionisation, but with enough energy to raise the molecule to an excited state quantum state, this is known as the Franck-Hertz effect and is illustrated in Figure 18 [53].

Figure 18: Excitation-relaxation photon emission

As the molecule spontaneously relaxes back to a ground state the excess energy is released as a photon whose frequency will give the plasma its colour, the amount of energy released can be expressed by equation 2.1

$$E = hv ag{2.1}$$

Where E (J) is the energy of the electron, h (J·s) is Planck's constant (6.62606957  $\times 10^{-34}$ ), v (Hz) is the frequency of the photon [54].

#### 2.4.5 Dissociation

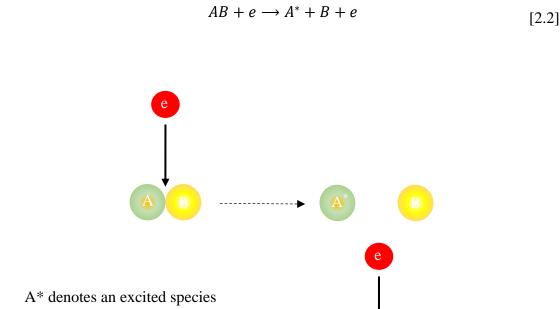

A further process that occurs within the plasma is the production of free radicals which are molecular fragments with unpaired electrons and are highly reactive in an etch environment. The free radicals are created in a plasma reactor by a method known as dissociation by electron impact, where a free electron hits a molecule and breaks the molecular bonds holding the atoms together resulting in the formation of free radicals that can be expressed in equation 2.2 and is shown in Figure 19 [46].

Figure 19: Dissociation by electron impact

Fluorine free radicals are chemically very reactive and will spontaneously etch silicon on contact through a process of adsorption of radicals, chemical reaction with the substrate and desorption of the waste reaction products [55]. The resulting etch profile produced using only radicals will be isotropic in nature and will have no directionality, this process will provide the bulk of the material removal with the ions producing the profile fine tuning (anisotropic part of the etch).

The gas used to produce the etch profiles in this DoE was sulphur hexafluoride (SF<sub>6</sub>) which is widely employed as an etchant because it is a highly reactive at low temperatures, with fast etch rates

that do not damage the surface of the substrate undesirably [56].  $SF_6$  will readily dissociate in the plasma by the mechanisms illustrated in Table 4 [57].

Table 4: SF<sub>6</sub> Dissociation mechanism

| SF <sub>6</sub> +e | $\rightarrow$ | SF <sub>5</sub> +F+e                  |

|--------------------|---------------|---------------------------------------|

| SF <sub>6</sub> +e | $\rightarrow$ | SF <sub>4</sub> +2F+e                 |

| SF <sub>6</sub> +e | $\rightarrow$ | SF <sub>4</sub> +F <sub>2</sub> +e    |

| SF <sub>6</sub> +e | $\rightarrow$ | SF <sub>3</sub> +3F+e                 |

| SF <sub>6</sub> +e | $\rightarrow$ | SF <sub>3</sub> +F+F <sub>2</sub> +e  |

| SF <sub>6</sub> +e | $\rightarrow$ | SF <sub>2</sub> +4F+e                 |

| SF <sub>6</sub> +e | $\rightarrow$ | SF <sub>2</sub> +2F+F <sub>2</sub> +e |

| SF <sub>6</sub> +e | $\rightarrow$ | SF <sub>2</sub> +2F <sub>2</sub> +e   |

| SF <sub>6</sub> +e | $\rightarrow$ | SF+5F+e                               |

| SF <sub>6</sub> +e | $\rightarrow$ | SF+3F+F <sub>2</sub> +e               |

| SF <sub>6</sub> +e | $\rightarrow$ | SF+F+2F <sub>2</sub> +e               |

|                    |               |                                       |

# 2.5 Dry Plasma Etching

Plasma etching is achieved using surface chemistry that mainly consists of 3 steps:

- 1. Adsorption of radicals from the reactor environment.

- 2. The reaction between the silicon and fluorine.

- 3. Subsequent desorption of reaction products.

This reaction typically results in an anisotropic etch profile [55] and is achieved by creating a stable plasma inside a vacuum chamber between a pair of metal plates referred to as an anode (+) and cathode (-). Reactive gas and radio frequency (RF) energy are injected into the vacuum chamber producing a gas glow discharge to generate the reactive species that are needed to facilitate the removal of the surface of the substrate that is exposed by open areas in the mask.

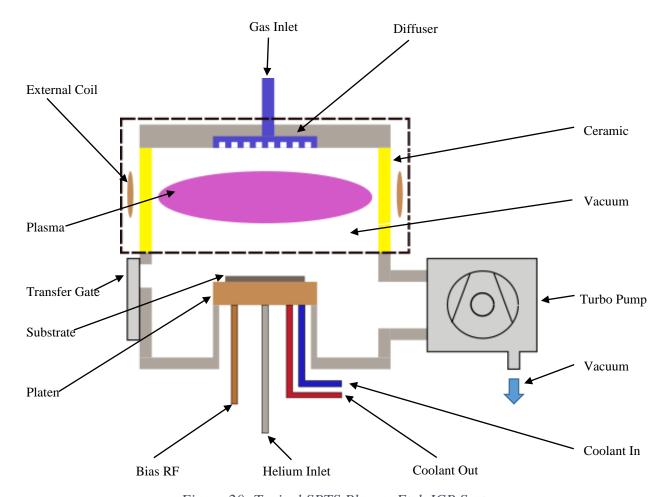

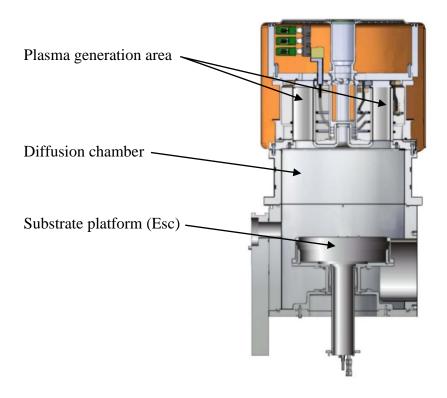

Figure 20: Typical SPTS Plasma Etch ICP System

The type of plasma etching chamber shown in Figure 20 is known as an inductively coupled plasma (ICP) reactor and it is of the type that will be utilised for this project.

Reactive gas is injected into the vacuum pressure vessel via the top cover of the source and passes through a diffuser which is designed to give a conformal spread of the gas into the chamber. An external coil is mounted around the outside of the ceramic pressure vessel to which RF power is applied at a frequency of 13.56 MHz which is the Federal Communications Commission (FCC) standard allocated frequency for Industrial, Scientific and Medical (ISM) equipment [58]. The RF power circulates around the coil which in turn causes a magnetic field to be generated that permeates the ceramic wall resulting in a plasma being formed inside the pressure vessel.

An ICP reactor causes a plasma to be formed inside the pressure vessel which consists of high levels of etch reactive species and charged particles. Variations in the coil RF power have a direct effect on the plasma density, with the ion energy being independently controlled via voltage bias control of the substrate. This bias control is made possible as the substrate is placed onto a platform (platen) that is driven by an independent RF power supply, the bias generator places either low frequency (380 KHz) [58] or high frequency (13.56 MHz) RF power onto the platen at a negative polarity. This attracts and accelerates the positively charged free ions present in the plasma towards the substrate, thus performing the physical part of the edge that leads to an anisotropic etch profile.

The wafer is held in place by a bi-polar electrostatic chuck (ESC), an assembly that uses two separate, biased metal plates that have opposing charges with a variable 6Kv to 12Kv potential difference, this establishes an electrostatic charge between the two plates that clamps the substrate tightly (chucking) onto the surface of the ESC as long as the voltage is maintained [59]. The substrate is kept at the processing temperature by combining two methods of cooling, the first being a chilled, non-conductive fluid flowing through the ESC to maintain a constant temperature, and the second component being helium gas (at a pressure between 6 and 20Torr) that is fed into the area between the

surface of the Esc and the chuck to act as a heat transfer mechanism that quickly conducts heat from the surface of the substrate into the cooling fluid flowing within the platen body. Without this cooling facility the substrate surface would rapidly overheat due to ion bombardment and plasma temperature, resulting in permanent device damage or destroying any mask that is present on the wafer.

The degree of anisotropy during the etch process depends on the specific plasma/material interactions that are occurring within the process chamber, as explained earlier in this section the etching process consists of three steps, adsorption, reaction, and desorption of the reaction products. If these three effects alone are present in the process, etching will occur spontaneously but the etch profile will be isotropic, in order to change the etch profile to anisotropic the etch step can be assisted by ion impact driven by the level of bias RF introduced into the vacuum chamber [55].

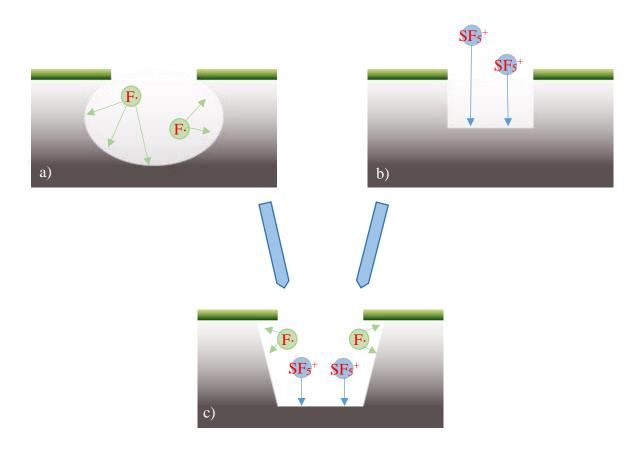

In an ICP reactor a typical etch gas used to etch Si is sulphur hexafluoride (SF<sub>6</sub>), this is introduced into the chamber and is subjected to the magnetic fields that ignite the plasma. Ultimately a free electron strikes an SF<sub>6</sub> molecule which removes an electron and a fluorine (F) atom resulting in an SF<sub>6</sub> ion, a fluorine free radical (F\*) and a free electron. The free electron that is released by this exchange is accelerated by the magnetic fields inducing the plasma and continues the chain reaction that is occurring within the process chamber. The SF<sub>6</sub> ion (see Table 4) [60] is now positively charged and the negative bias voltage is used to accelerate the ion into the surface of the substrate to produce the anisotropic trench profile. The fluorine free radical released is highly reactive and will freely react with the substrate surface but will only produce an isotropic trench profile [55]. Using the combined effects from both types of etching that occur on the surface of the substrate it is possible to achieve the positive etch profile taper that is required for this programme of work, the mechanisms involved in this process can be seen in Figure 21.

Figure 21: Etching Types and the Resulting Profiles (a) Chemical etching by fluorine radicals, (b) Physical etching by  $SF_6$  ions, (c) Positive profile resulting from combined etching [46]

### 2.5.1 Edge Loading

Edge loading or 'macro loading' as it's sometimes described, is a wafer level loading effect where the etching ability of the chamber environment is enhanced by a lack of substrate material over a local area. An area near the centre of a substrate will have material fully surrounding it and as a result the reactive species (ions and radicals) are evenly spread across the surface of the material. At the edge of the substrate, it will have material to the inside of the edge but no material to the outside, the result of this is that the ions being attracted downwards will hit the substrate but will pass without effect outside of the substrate area. The radicals that are not driven by the bias power, will etch the surface of the substrate as they contact it. Beyond its edge they are still present in the environment and will act

as a reservoir to top up the radicals being consumed during the process, locally increasing the etch rate of the TSV's around the edge [61].

#### 2.5.2 Wet and Dry Etching Comparison

The decision for which method to use for the etching of silicon is entirely dependent on the desired result of the production process as each technique has its own strengths and weaknesses. Wet etching has much less expensive and simpler process equipment that is comparatively easy to scale to industrial levels. It produces a very high etch rate and has good material selectivity, but it does have the drawbacks that the etch process and device profile are difficult to control as the etch always produces the classic isotropic 'strawberry' shape. The chemicals used to produce the etch are toxic, expensive, and needed in large quantities, for many wet etching manufacturing tasks the treatment and disposal costs of process effluent often surpasses the manufacturing costs, increasing restrictions on waste disposal and landfill are leading to process improvements that reduce the environmental toll that can result from wet etch processes [62].

Dry etching, by comparison can control the etch depth and shape to a very high degree of accuracy and can produce small delicate structures. Any toxic or hazardous by-products of the etch process can be removed by a cleaning process within the same process chamber and surface conditioning can be used to prevent corrosion of the substrate when exposed to air [63]. Dry etching has significant financial drawbacks over wet etching as the equipment is expensive to purchase and requires trained, experienced technicians to ensure that the systems remain operational. Scaling up to industrial levels requires a large capital investment which can be out of reach for smaller manufacturers.

When choosing a manufacturing method consideration should be given to the above factors, in addition to: -

- The numbers of devices to be manufactured.

- Do the devices have small delicate features?

- What tolerances are adequate for the requirements of the product.

- The amount of capital available to purchase or modify existing equipment.

- Cost of ownership of the etch equipment.

For the purposes of this project the only real option was dry plasma etching as the required device profile control needed for both depth and sidewall angle to achieve the desired results is relatively simple to attain. Similar results would be difficult to achieve with wet etching as the etch rates are normally far too slow for production applications and precise alignment to the substrate crystal plane is needed to ensure that the correct profile shape and depth are achieved [64].

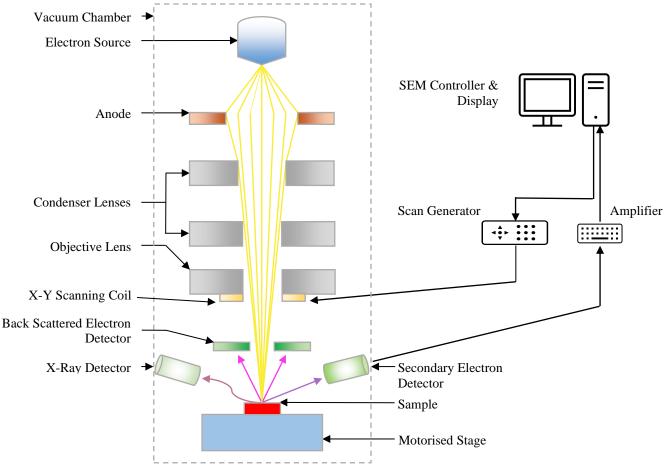

# 2.6 Scanning Electron Microscope (SEM)

The TSV features that were produced during this research project are too small to be seen with the naked eye, as a result of this some form of microscope was required to view and measure the etched profiles. The most common type of microscope available is an optical microscope which uses visible light to view a sample through a series of lenses, unfortunately this type of device is limited to profiles larger than 25µm as this is its lower resolution limit [65]. The TSV profiles produced for this project are often smaller than the lower limit of an optical microscope so another method to view and measure the device dimensions was found.

A less common microscope that is frequently used in semiconductor applications is the scanning electron microscope (SEM), this type of device has a lower resolution limit of around 0.2nm and can focus on more than one part of a feature at the same time, this allows the microscope to produce 3D images of the sample, although the resulting image is a digital reconstruction rather than the direct image that an optical microscope produces [66].

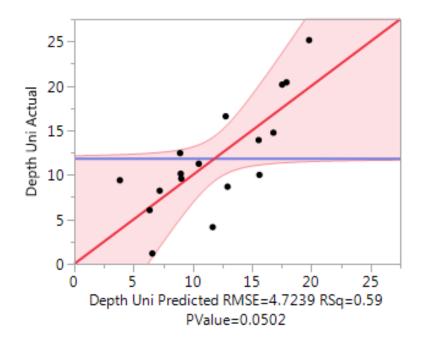

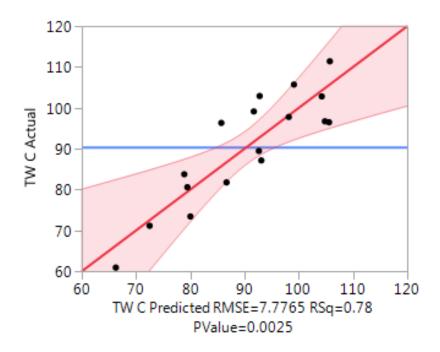

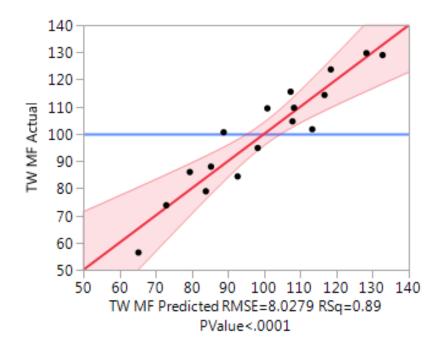

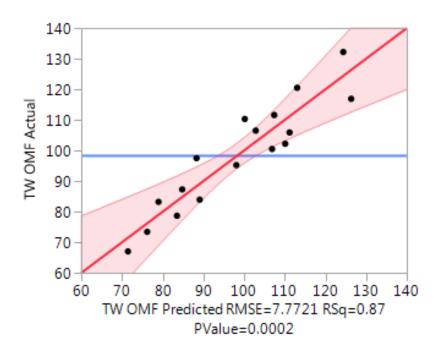

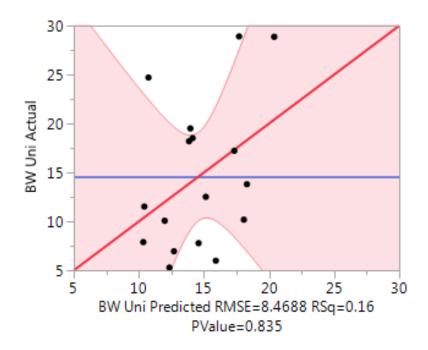

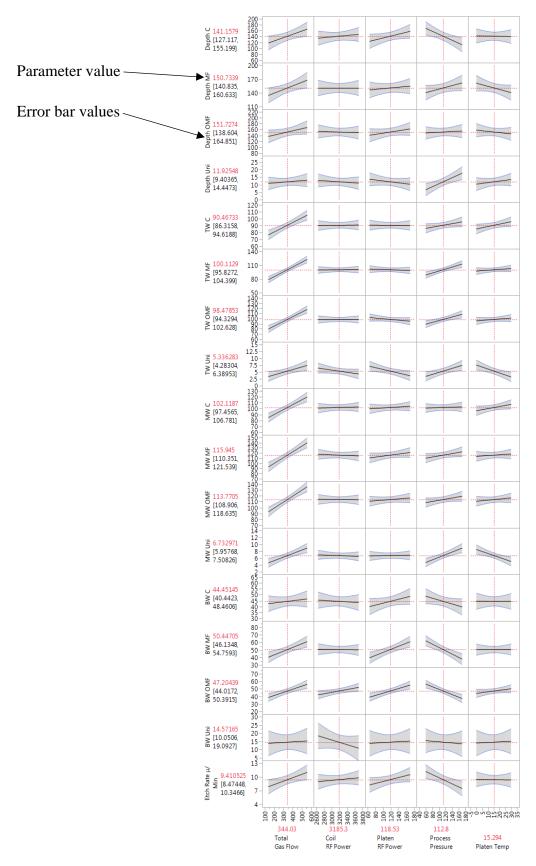

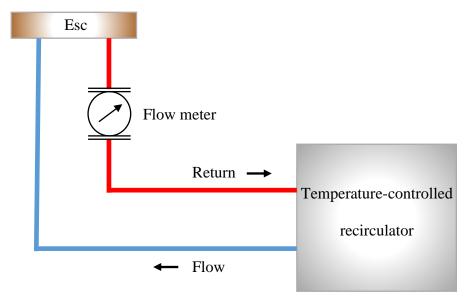

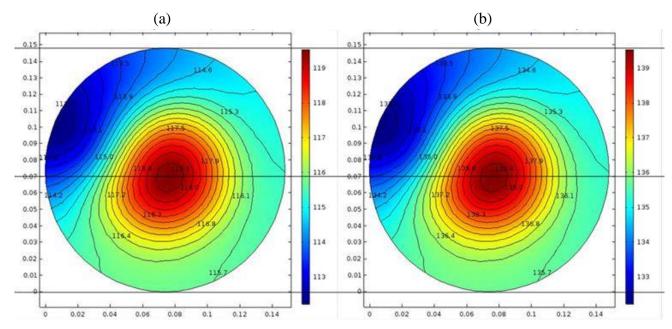

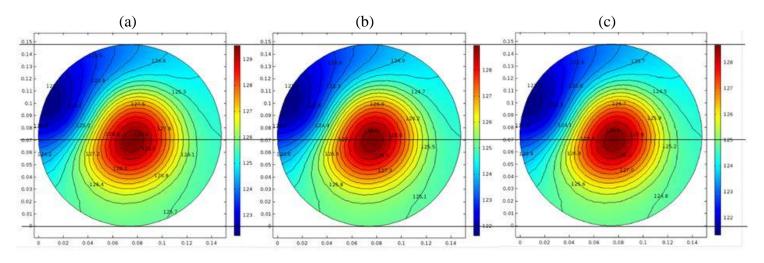

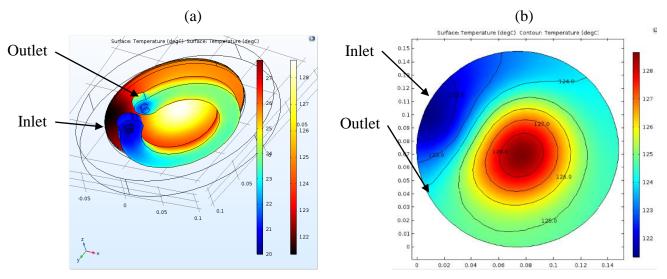

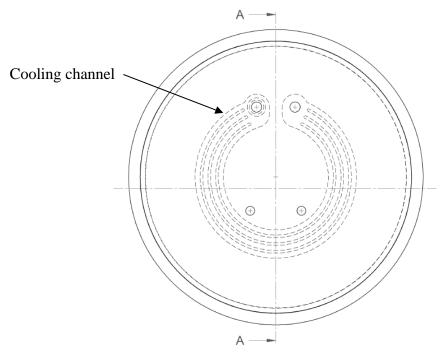

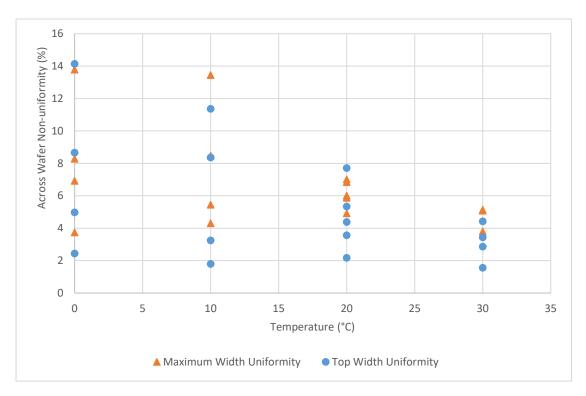

The TSV feature dimensions that produced using the process conditions detailed in Table 6 are frequently smaller than  $5\mu m$ , as a result it was decided that a SEM was a more appropriate measuring device for use in this project.