# Development of Silicon Carbide Devices for Next-Generation Surge Protection and Power Electronics

## Finn Monaghan

Department of Electrical and Electronic Engineering

Swansea University

This dissertation is submitted for the degree of Engineering Doctorate

June 2025

Copyright: The Author, Finn Monaghan, 2025.

## **Declaration**

| Declarations                                                                                                                                                                         |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| This work has not previously been accepted in substance for any degree and is no concurrently submitted in candidature for any degree.                                               | ot being |

| Signed:                                                                                                                                                                              |          |

| Date: 20/01/2025                                                                                                                                                                     |          |

| This thesis is the result of my own investigations, except where otherwise state Other sources are acknowledged by footnotes giving explicit references. A bibliography is appended. | d.       |

| Signed:                                                                                                                                                                              |          |

| Date: 20/01/2025                                                                                                                                                                     |          |

| I hereby give consent for my thesis, if accepted, to be available for electronic shaped:                                                                                             | aring    |

| Date: 20/01/2025                                                                                                                                                                     |          |

| The University's ethical procedures have been followed and, where appropriate ethical approval has been granted.                                                                     | e, that  |

| Signed:                                                                                                                                                                              |          |

| Date: 20/01/2025                                                                                                                                                                     |          |

## Acknowledgements

Firstly, I would like to thank both of my EngD supervisors: Professor Mike Jennings and Associate Professor Antonio Martinez. Without both of them, completing this EngD in the exciting field of Silicon Carbide power devices, which has exposed me to cutting edge technology and physics would not have been possible. In particular, I'd like to thank Mike for always having an open door to offer guidance, and for lending his extensive expertise in SiC during many insightful conversations. Mike - I can't thank you enough, I look forward to working with you in the future!

I also must give huge thanks to Antonio, who showed me (and schooled me) in the art of simulating semiconductor devices. The extensive meetings and whiteboard drawings in his office definitely taught me almost all of what I have learnt and understand about semiconductor physics. Antonio - I hope one day I can pass this knowledge onto someone else, and I'm at least half as good at it as you.

Next, I must also thank Dr Jon Evans, who's insight and help with mask and process design was invaluable. Jon has offered me guidance on all aspects of my fabrication and characterisation work, and I have benefited greatly from his knowledge and assistance in the cleanroom and in the electrical test lab. I hope our professional relationship will continue long into the future, even if involves GaN.

For critiquing my lunch choices and educating me on sumo wrestling, I would like to thank Dr Ryan Bigham, Mark Williams and Dan Winkley. Dan may be the terror of the Tesco's reduced section, but him and Gareth Blayney almost single-handedly kept the building lights on, and us cleanroom users alive - thank you both.

I would also like to extend my gratitude to internal collaborators Nick Burridge, and Dr. Ahmed Ben Khaial for assisting me with wafer dicing and metal deposition requirements respectively throughout the project. I also wish to thank our outside collaborators at IMB-CNM Barcelona, lead by Dr Amador Peréz-Tomás for assistance with SiC activation annealing.

Finally, I would like to thank my family for the never-ending support and inspiration for me to finish this degree. Without you, I would've never been able to come this far without your understanding and help. You've always believed in me, and I can't thank you enough.

## **Abstract**

Silicon Carbide (SiC) power devices are becoming popular in a variety of different applications, however one un-tapped sector for SiC is the circuit protection market. Specifically depletion-mode SiC JFETs could be utilised in over-current/voltage protection products such as Bourns' *Transient Blocking Unit* (TBU®) product line to enhance efficiency, and penetrate previously unfeasible high voltage markets.

This thesis investigates and begins the development of 4H-SiC JFETs specifically designed for the TBU® application. Extensive optimisation of the JFET cell and termination design are explored using finite-element simulations. The trade-off between JFET off-state performance and design parameters is identified.

For the first time, Short Channel Effects (SCEs) are comprehensively shown to affect JFET behaviour when the channel length is short. In particular, JFET breakdown voltage can be degraded to only 50V for a 1200V drift region if channel length is short. It is demonstrated that by introducing sidewall P-type implants, the JFET channel can be extended without requiring high implantation energies, and completely eliminates the premature device failure caused by SCEs. This is demonstrated to improve breakdown voltage by 1000V in some cases.

A new 4H-SiC JFET design integrating a temperature sensor on the semiconductor surface is also demonstrated using finite-element simulations. The sensor consists of a lateral P-type resistor formed simultaneously with the P+ gate junction. Electrothermal simulations were employed to consider device self-heating effects showed the sensor had an  $R^2$  of 0.996, which is comparable to other 4H-SiC temperature sensors. The sensor was also shown to be stable under high drain bias when blocking, with  $I_{sens}$  only varying by 4% between  $V_d$ = 0V and 1000V.

Process optimization was also completed on three key elements of the JFET fabrication process: carbon capping layers used for surface protection, P-type implant activation, and P-type ohmic contacts. The P+ gate junction is a fundamental part of the JFET unit cell structure. It was found that  $T_{anneal}$ = 1700°C resulted in the highest percentage of implanted dopants becoming electrically, with 26.9% activation. Furthermore, it was also found that

ohmic contacts using the Ti/Al/Ni metal scheme offered the lowest specific contact resistivity of  $4.91 \times 10^{-6} \Omega cm^2$ , which was achieved after annealing at  $1050^{\circ}$ C for 2 minutes.

## **List of Publications**

#### **Journal Publications**

- [1] F. Monaghan, A. Martinez, J. Evans, C. Fisher, and M. Jennings, "On short channel effects in high voltage jfets: A theoretical analysis," *Power Electronic Devices and Components*, vol. 7, p. 100057, 2024.

- [2] F. Monaghan, A. Martinez, J. Evans, C. Fisher, and M. Jennings, "A 4h-sic jfet with a monolithically integrated temperature sensor," *Power Electronic Devices and Components*, vol. 8, p. 100069, 2024.

- [3] F. Li, F. Roccaforte, G. Greco, P. Fiorenza, F. La Via, A. Pérez-Tomas, J. E. Evans, C. A. Fisher, F. A. Monaghan, P. A. Mawby, *et al.*, "Status and prospects of cubic silicon carbide power electronics device technology," *Materials*, vol. 14, no. 19, p. 5831, 2021.

#### **Conference Publications**

- [1] F. Monaghan, A. Martinez, C. Fisher, and M. Jennings, "Impact of dimensions and doping on the breakdown voltage of a trench 4h-sic vertical jfet," *Key Engineering Materials*, vol. 948, pp. 69–75, 2023.

- [2] F. Monaghan, A. Martinez, J. E. Evans, C. Fisher, O. J. Guy, and M. Jennings, "Design of monolithically integrated temperature sensors in 4h-sic jfets," *Key Engineering Materials*, vol. 984, pp. 47–54, 2024.

- [3] B. Jones, J. Mitchell, J. Evans, F. Monaghan, M. Jennings, C. Bolton, K. Riddel, H. Ashraf, and O. J. Guy, "Introducing foundry-compatible sic and gan trench processing technologies for reliable automotive application," in *Materials Science Forum*, vol. 1062, pp. 582–587, Trans Tech Publ, 2022.

- [4] B. Jones, A. Croot, J. Mitchell, C. Bolton, J. E. Evans, F. Monaghan, K. Riddell, M. Jennings, O. J. Guy, and H. Ashraf, "Demonstrating sic in situ rounded trench processing technologies for future power trench mosfet applications," *Solid State Phenomena*, vol. 359, pp. 163–170, 2024.

- [5] J. Evans, J. Patel, A. Ben Khaial, N. Burridge, R. Hyndman, F. Monaghan, M. Jennings, H. Ashraf, R. Harper, and M. Elwin, "Fabrication of quasi-vertical gan-on-sic trench mosfets," *Key Engineering Materials*, vol. 945, pp. 61–66, 2023.

## **Table of contents**

| Li | st of f | igures    | 2                                             | ΚV |  |  |  |

|----|---------|-----------|-----------------------------------------------|----|--|--|--|

| Li | st of t | ables     | xx                                            | ix |  |  |  |

| No | omen    | clature   | xx                                            | xi |  |  |  |

| 1  | Intr    | roduction |                                               |    |  |  |  |

|    | 1.1     | Backg     | round                                         | 1  |  |  |  |

|    | 1.2     | Wide 1    | Bandgap Semiconductors: Comparing to Silicon  | 2  |  |  |  |

|    |         | 1.2.1     | Preface                                       | 2  |  |  |  |

|    |         | 1.2.2     | Bandgap Energy                                | 2  |  |  |  |

|    |         | 1.2.3     | Electric Field and Breakdown Voltage          | 5  |  |  |  |

|    |         | 1.2.4     | Unipolar Limit                                | 8  |  |  |  |

|    |         | 1.2.5     | State of the Art: GaN                         | 10 |  |  |  |

|    |         | 1.2.6     | State of the Art: SiC                         | 12 |  |  |  |

|    | 1.3     | Overv     | iew of Surge Protection Technology            | 15 |  |  |  |

|    | 1.4     | Introd    | uction to Cascodes                            | 17 |  |  |  |

|    | 1.5     | Motiva    | ation                                         | 20 |  |  |  |

|    | 1.6     | Thesis    | Overview                                      | 20 |  |  |  |

| 2  | Ana     | lytical I | Modelling and Physical Models                 | 23 |  |  |  |

|    | 2.1     | Prefac    | e                                             | 23 |  |  |  |

|    | 2.2     | Analy     | tical Modelling                               | 23 |  |  |  |

|    |         | 2.2.1     | JFET Resistance Model                         | 23 |  |  |  |

|    |         | 2.2.2     | A Carrier Storage Layer                       | 29 |  |  |  |

|    |         | 2.2.3     | HEMT Resistance Model                         | 31 |  |  |  |

|    |         | 2.2.4     | Comparing SiC JFETs and GaN HEMTs             | 34 |  |  |  |

|    | 2.3     | Physic    | al Models used in Drift-Diffusion Simulations | 36 |  |  |  |

|    |         | 2.3.1     | The Anisotropic Nature of 4H-SiC              | 36 |  |  |  |

**xii** Table of contents

|   |      | 2.3.2   | Drift Diffusion and Current Continuity                | 38  |

|---|------|---------|-------------------------------------------------------|-----|

|   |      | 2.3.3   | Carrier Recombination                                 | 39  |

|   |      | 2.3.4   | Impact Ionization                                     | 42  |

|   |      | 2.3.5   | Incomplete Ionization                                 | 42  |

|   |      | 2.3.6   | Carrier Mobility                                      | 44  |

|   |      | 2.3.7   | High Field Saturation                                 | 45  |

|   |      | 2.3.8   | Thermodynamic Model                                   | 46  |

|   | 2.4  | Conclu  | usion                                                 | 47  |

| 3 | Desi | gn and  | Simulation of 4H-SiC JFETs                            | 49  |

|   | 3.1  | Prefac  | e                                                     | 49  |

|   | 3.2  | Calibr  | ating Simulations                                     | 49  |

|   | 3.3  | Short   | Channel Effects in JFETs                              | 52  |

|   |      | 3.3.1   | Device Structure                                      | 53  |

|   |      | 3.3.2   | On-State Characterisation                             | 56  |

|   |      | 3.3.3   | Isolating the Effect of Junction Depth                | 60  |

|   |      | 3.3.4   | Breakdown Voltage                                     | 67  |

|   |      | 3.3.5   | Summary                                               | 76  |

|   | 3.4  | Introd  | ucing Sidewall Implantation                           | 76  |

|   |      | 3.4.1   | Introduction                                          | 76  |

|   |      | 3.4.2   | Comparison to Non-Sidewall Implanted JFET             | 77  |

|   |      | 3.4.3   | Varying Mesa Height                                   | 80  |

|   |      | 3.4.4   | Achieving Sidewall Doping Without Tilted Implantation | 82  |

|   |      | 3.4.5   | Summary                                               | 84  |

|   | 3.5  | Edge 7  | Termination: Floating Field Rings                     | 85  |

|   |      | 3.5.1   | Constant Ring Spacing                                 | 87  |

|   |      | 3.5.2   | Incremental Ring Spacing                              | 90  |

|   |      | 3.5.3   | Sensitivity to Interface Charge                       | 92  |

|   | 3.6  | Conclu  | usion                                                 | 94  |

| 4 | A JI | FET wit | th a Monolithically Integrated Temperature Sensor     | 97  |

|   | 4.1  | Prefac  | e                                                     | 97  |

|   | 4.2  | A Rev   | iew of SiC Temperature Sensors                        | 97  |

|   | 4.3  | Integra | ating a Temperature Sensor with a SiC JFET            | 98  |

|   | 4.4  | Funda   | mentals of Sensor Operation                           | 99  |

|   |      | 4.4.1   | Incomplete Ionization                                 | 101 |

|   |      | 4.4.2   | Hole Mobility                                         | 102 |

Table of contents xiii

|   |      | 4.4.3             | Resistivity and Resistance                                  |

|---|------|-------------------|-------------------------------------------------------------|

|   | 4.5  | Compar            | ing to TCAD                                                 |

|   |      | 4.5.1             | Considering Contact Resistance                              |

|   | 4.6  | On-State          | e Behaviour                                                 |

|   | 4.7  | Transier          | nt Behaviour                                                |

|   | 4.8  | Off-Stat          | e                                                           |

|   | 4.9  | Conclus           | ion                                                         |

| 5 | Cor  | relating <b>I</b> | Material Defects with Unipolar Device performance 123       |

|   | 5.1  | Preface           |                                                             |

|   | 5.2  | A Revie           | w of Material Defects in 4H-SiC                             |

|   |      | 5.2.1             | Defect Detection Methods                                    |

|   | 5.3  | Method            | ology                                                       |

|   |      | 5.3.1             | Mapping SiC Wafers for Defects                              |

|   |      | 5.3.2             | Fabrication of Schottky Barrier Diodes                      |

|   |      | 5.3.3             | Characterisation of 150mm SiC SBD wafers                    |

|   |      | 5.3.4             | Methods to Determine Barrier Height and Ideality Factor 130 |

|   | 5.4  | Results           | and Analysis                                                |

|   |      | 5.4.1             | Forward Bias                                                |

|   |      | 5.4.2             | Reverse Bias                                                |

|   | 5.5  | Conclus           | ion                                                         |

| 6 | Proc | ess Deve          | lopment for 4H-SiC JFET Fabrication 147                     |

|   | 6.1  | Preface           |                                                             |

|   | 6.2  | Charact           | erisation Methods                                           |

|   |      | 6.2.1             | Contact Resistance                                          |

|   |      | 6.2.2             | Electrical Activation of Dopants                            |

|   | 6.3  | Develop           | ment of Carbon Caps for Surface Protection                  |

|   |      | 6.3.1             | Formation of Carbon Cap                                     |

|   |      | 6.3.2             | Carbon Cap Removal                                          |

|   | 6.4  | P-type A          | Activation and Ohmic Contact Study                          |

|   |      | 6.4.1             | Fabrication Process                                         |

|   |      | 6.4.2             | Hall Characterisation Results                               |

|   |      | 6.4.3             | Ohmic Contact Results                                       |

|   |      | 6.4.4             | Temperature Dependence of Ohmic Contacts                    |

|   | 6.5  | Conclus           | ion                                                         |

**xiv** Table of contents

| 7  | Con   | clusion | and Future Work                                    | 173 |

|----|-------|---------|----------------------------------------------------|-----|

|    | 7.1   | Concl   | lusion                                             | 173 |

|    | 7.2   | Futur   | e Work                                             | 174 |

|    |       | 7.2.1   | Simulation                                         | 175 |

|    |       | 7.2.2   | Fabrication and Characterisation                   | 175 |

| Re | feren | ices    |                                                    | 177 |

| Aį | pend  | lix A   | Python Code for Heatmaps of Device Characteristics | 197 |

| Aı | pend  | lix B   | RCA Sample Clean Procedure                         | 207 |

| Aı | pend  | lix C   | SiC JFET Mask Layout and Process Flow              | 209 |

# **List of figures**

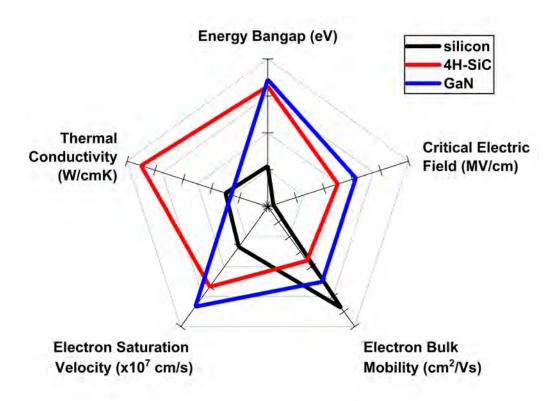

| 1.1  | Radar plot of key material properties of all three semiconductors, using          |    |

|------|-----------------------------------------------------------------------------------|----|

|      | values from table 1.1                                                             | 3  |

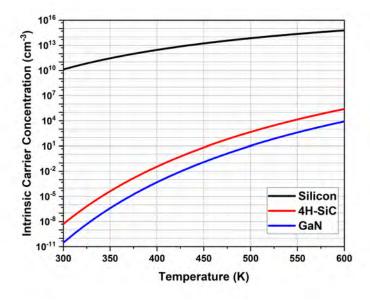

| 1.2  | Intrinsic carrier concentration plotted against temperature for silicon, 4H-SiC   |    |

|      | and GaN                                                                           | 4  |

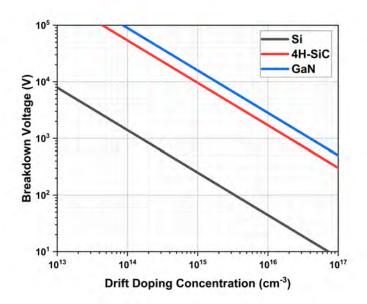

| 1.3  | Parallel plane breakdown voltage plotted as a function of drift doping con-       |    |

|      | centration for silicon, 4H-SiC and GaN                                            | 6  |

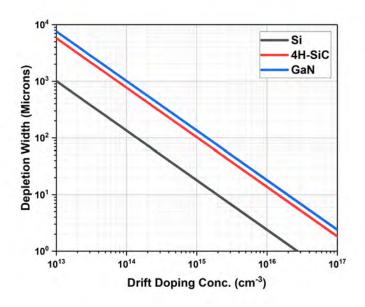

| 1.4  | Parallel plane depletion width plotted as a function of drift doping for silicon, |    |

|      | 4H-SiC and GaN                                                                    | 7  |

| 1.5  | Example cross-section of silicon, SiC and GaN layers designed to block the        |    |

|      | same voltage.                                                                     | 7  |

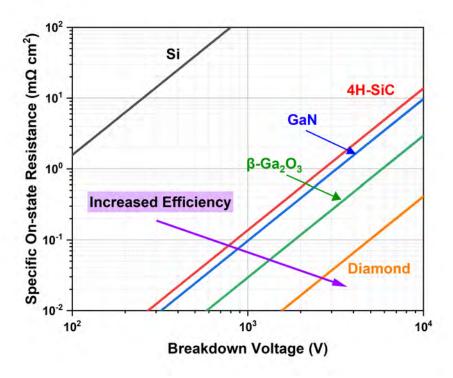

| 1.6  | The theoretical performance limits of unipolar devices for silicon and assorted   |    |

|      | wide bandgap materials                                                            | 9  |

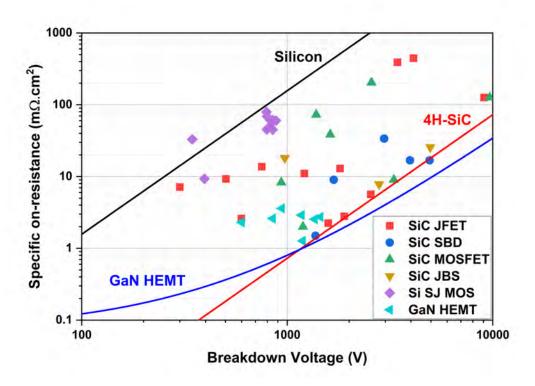

| 1.7  | Reported specific on-state resistance and breakdown voltages for GaN HEMTs,       |    |

|      | Si SJ MOSFETs and various SiC unipolar device types                               | 10 |

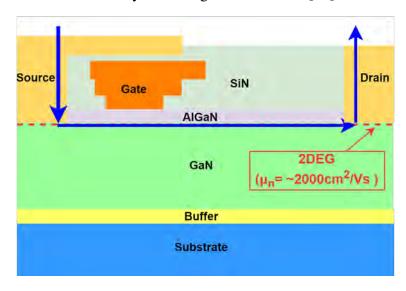

| 1.8  | Cross section of a typical depletion-mode GaN HEMT, with the current path         |    |

|      | indicated by blue arrows                                                          | 11 |

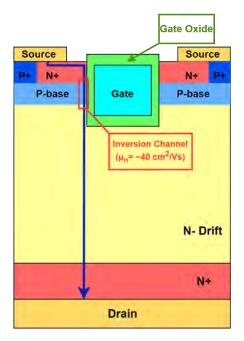

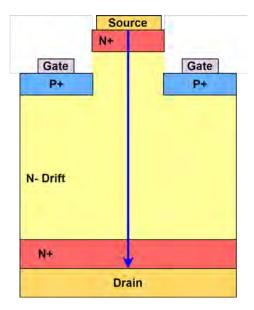

| 1.9  | Cross section of a Trench MOSFET device, with the current path shown              |    |

|      | indicated by a blue arrow                                                         | 13 |

| 1.10 | Cross section of a JFET device, with the current path shown indicated by a        |    |

|      | blue arrow.                                                                       | 14 |

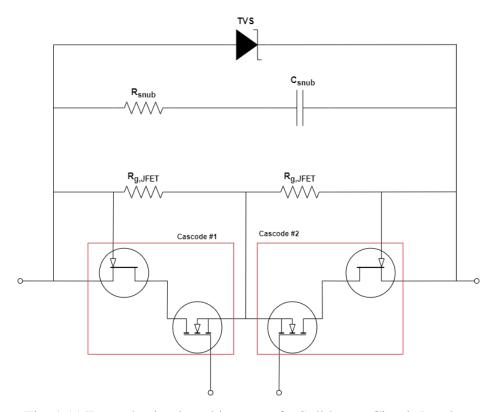

| 1.11 | Example circuit architecture of a Solid-state Circuit Breaker                     | 18 |

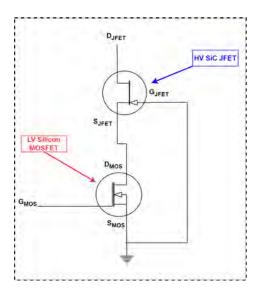

| 1.12 | The cascode circuit configuration of a SiC JFET and a low voltage silicon         |    |

|      | MOSFET                                                                            | 18 |

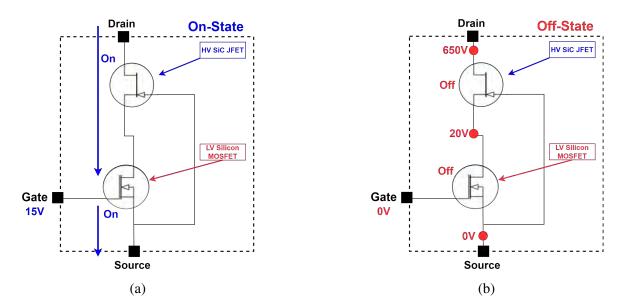

| 1.13 | A 650V Cascode in the (a) on-state, with current flow indicated by blue           |    |

|      | arrows, and (b) off-state, with potential at different points in the circuit      |    |

|      | indicated in red                                                                  | 19 |

xvi List of figures

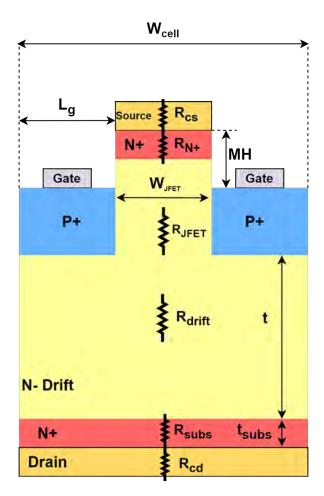

| 2.1  | A cross section of a JFET unit cell showing all resistance sources and relevant                |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | dimensions                                                                                     | 24 |

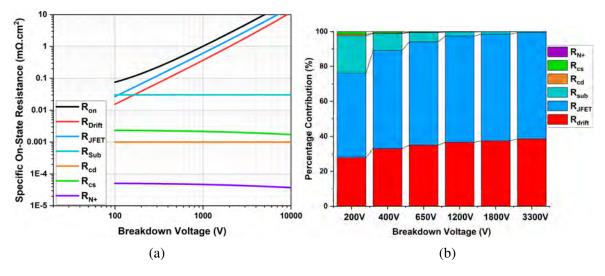

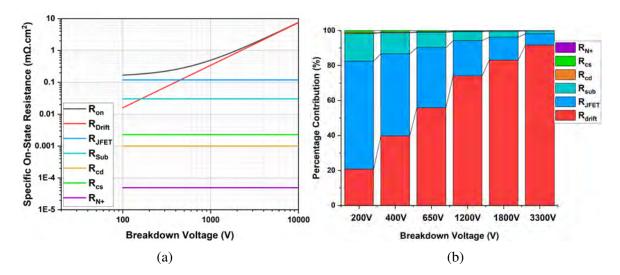

| 2.2  | (a) All sources of resistance plotted as a function of BV (b) Percentage                       |    |

|      | contributions of each resistance at selected BV values                                         | 26 |

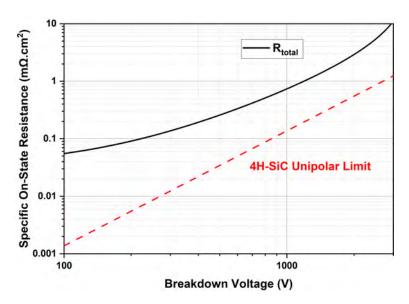

| 2.3  | A comparison of JFET $R_{on,sp}$ as calculated by the analytical model to the                  |    |

|      | 4H-SiC unipolar limit.                                                                         | 27 |

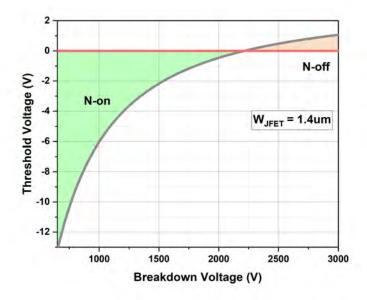

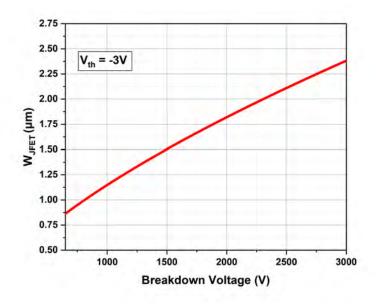

| 2.4  | Threshold voltage plotted as a function of $BV_{pp}$ for a constant $W_{JFET}$ of 1.4 $\mu$ m. | 28 |

| 2.5  | JFET region width required for $V_{th}$ = -3V for $BV_{pp}$ = 650 - 3000V                      | 29 |

| 2.6  | Cross section of a JFET unit cell, with a carrier storage layer introduced in                  |    |

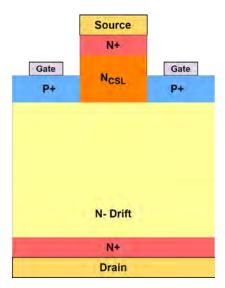

|      | the JFET Mesa region                                                                           | 30 |

| 2.7  | (a) All sources of resistance plotted as a function of BV for the CSL JFET                     |    |

|      | (b) Percentage contributions of each resistance at selected BV values                          | 31 |

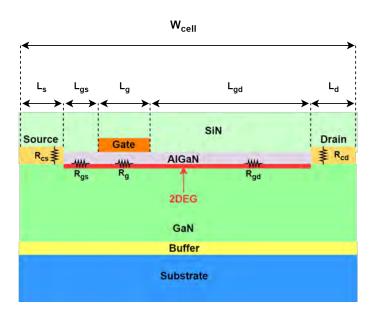

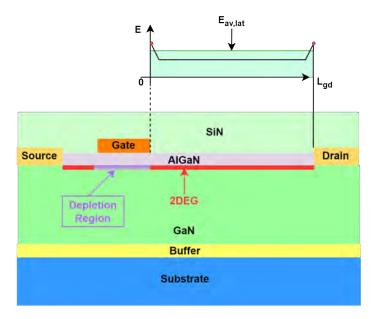

| 2.8  | A standard depletion-mode HEMT unit cell, with all sources of resistance                       |    |

|      | identified                                                                                     | 32 |

| 2.9  | HEMT in the off-state, showing an average electric field profile between the                   |    |

|      | gate and drain electrodes                                                                      | 33 |

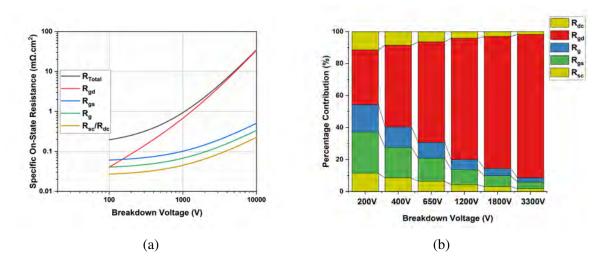

| 2.10 | (a) All sources of resistance plotted as a function of BV for a GaN HEMT                       |    |

|      | (b) Percentage contributions of each resistance at selected BV values                          | 34 |

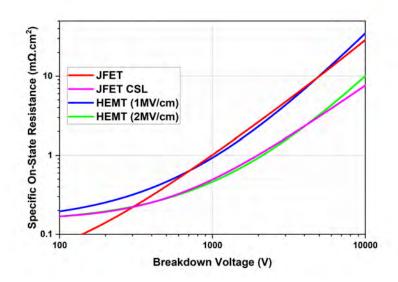

| 2.11 | Total specific on-resistance $R_{on}$ plotted against breakdown voltage for the                |    |

|      | standard JFET, CSL JFET and HEMT models                                                        | 35 |

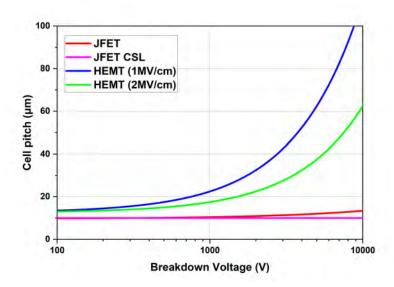

| 2.12 | Cell pitch plotted against breakdown voltage for the standard JFET, CSL                        |    |

|      | JFET and HEMT models                                                                           | 36 |

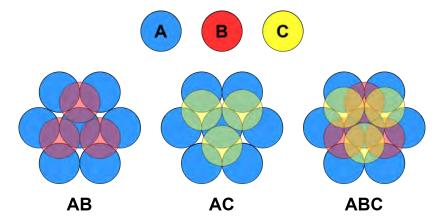

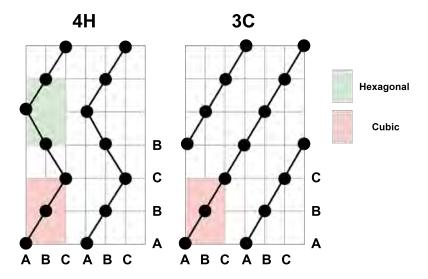

| 2.13 | The hexagonal packing arrangement in SiC consists of an initial SiC bilayer                    |    |

|      | labelled as A, followed by subsequent bilayers that can occupy either the B                    |    |

|      | or C positions                                                                                 | 37 |

| 2.14 | The different stacking arrangements of the 4H and 3C polytypes of SiC                          | 37 |

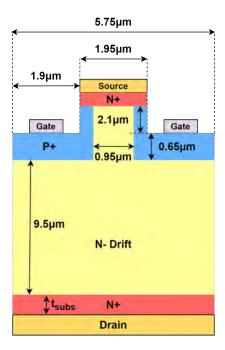

| 3.1  | The cross-section of the JFET unit cell reported by Zhao et al. to be replicated               |    |

|      | in Synopsys TCAD to calibrate simulations                                                      | 50 |

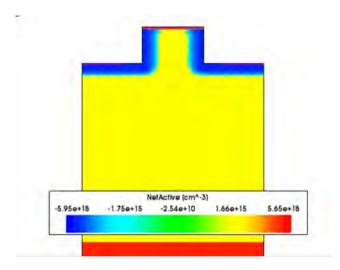

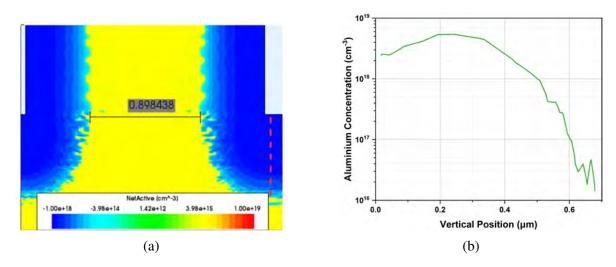

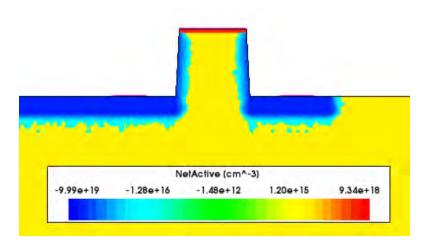

| 3.2  | The JFET unit cell of Zhao et al. recreated in TCAD, showing the net doping                    |    |

|      | profile                                                                                        | 51 |

| 3.3  | (a) A zoomed in image channel region of the JFET show in figure 3.2, show-                     |    |

|      | ing the measured channel width of $0.89\mu\mathrm{m}$ and the position of the vertical         |    |

|      | cut-line indicated by a red dashed line (b) The aluminium concentration                        |    |

|      | plotted along the length of the cut-line                                                       | 51 |

List of figures xvii

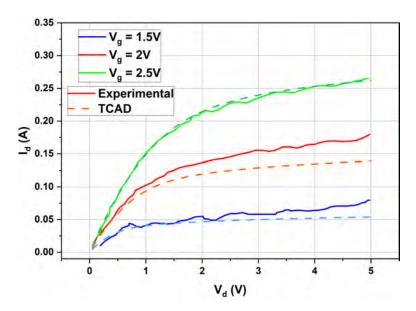

| 3.4  | Comparison of the experimental results of Zhao et al. and the simulated output characteristics using TCAD, at $V_g$ = 1.5V, 2V and 2.5V. Bulk electron |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | mobility has been set as $1140 \text{ cm}^2/Vs$                                                                                                        | 52 |

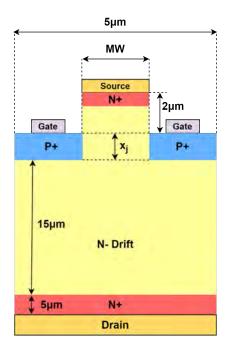

| 3.5  | The cross-section of the JFET unit cell used for TCAD simulation                                                                                       | 54 |

| 3.6  | Simulated SRIM depth profiles for each of the proposed implantation sched-                                                                             |    |

|      | ules shown in table 3.4.                                                                                                                               | 55 |

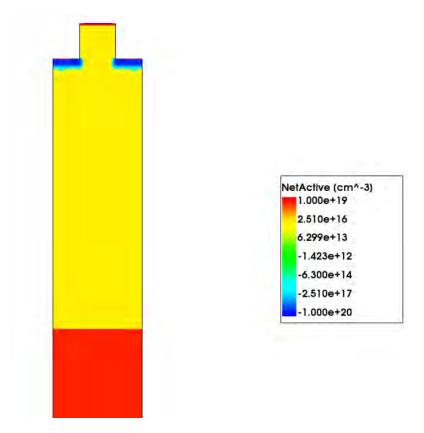

| 3.7  | Process simulated JFET unit cell with $x_i = 300$ nm                                                                                                   | 56 |

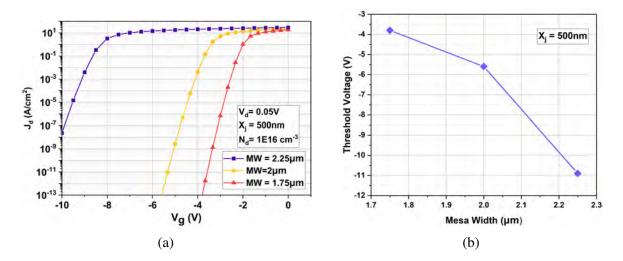

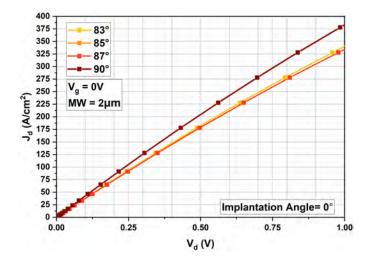

| 3.8  | (a) Transfer characteristics of design B ( $x_j$ = 500nm) with MW= 1.75 $\mu$ m,                                                                       |    |

|      | $2\mu$ m and $2.25\mu$ m (b) The corresponding $V_{th}$ values extracted for each mesa                                                                 |    |

|      | width tested. As MW increases, the JFET becomes increasingly harder to                                                                                 |    |

|      | switch off                                                                                                                                             | 57 |

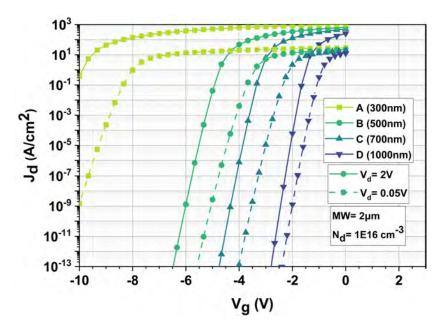

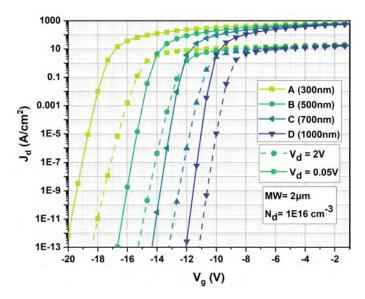

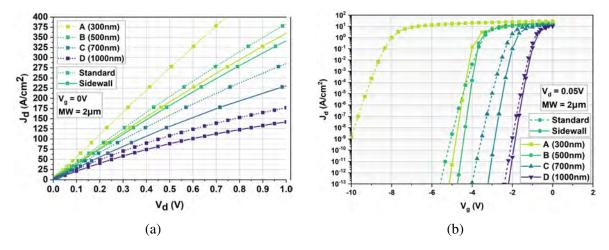

| 3.9  | Simulated transfer characteristics for all four designs at $V_d$ =0.05V and $V_d$ =2V.                                                                 |    |

|      | Larger channel lengths result in $V_{th}$ trending towards 0V. Longer channel                                                                          |    |

|      | lengths are also less sensitive to applied $V_d$ , indicating a reduced effect of                                                                      |    |

|      | DIBL                                                                                                                                                   | 58 |

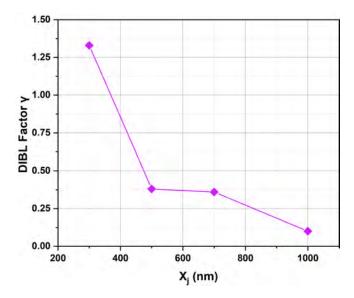

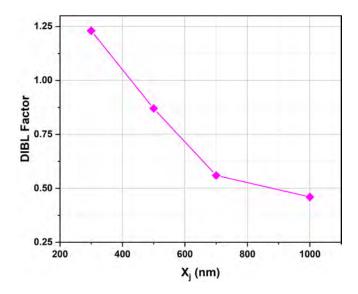

| 3.10 | Calculated DIBL factor $\gamma$ plotted as a function of $X_j$ . Increasing $X_j$ signifi-                                                             |    |

|      | cantly reduces $\gamma$ towards $0$                                                                                                                    | 59 |

| 3.11 | Doping profile of the JFET channel region of (a) Design A (b) Design D                                                                                 | 59 |

| 3.12 | The JFET half unit cell designed using Structure Editor to isolate the effect                                                                          |    |

|      | of $x_j$ from lateral straggling caused by implantation                                                                                                | 60 |

| 3.13 | Transfer characteristics of the JFET designed in structure editor for all values                                                                       |    |

|      | of $x_j$ at $V_d$ = 0.05V and 2V                                                                                                                       | 61 |

| 3.14 | The calculated DIBL factor for the ideal gate junction, plotted as a function                                                                          |    |

|      | of $X_j$                                                                                                                                               | 61 |

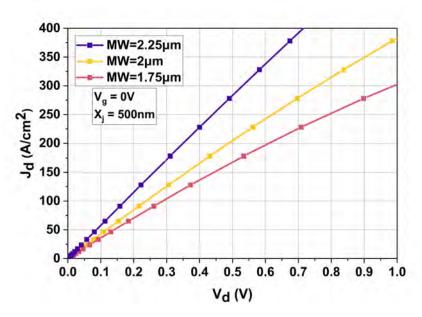

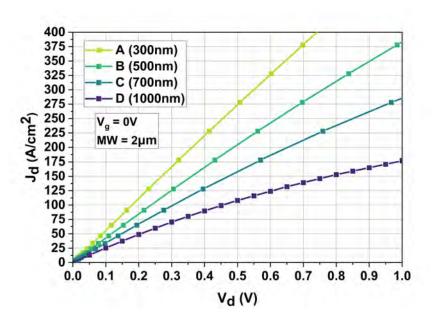

| 3.15 | Output characteristics at $V_g$ = 0V for design B with varying mesa width.                                                                             |    |

|      | $R_{on,sp}$ reduces at larger channel widths                                                                                                           | 62 |

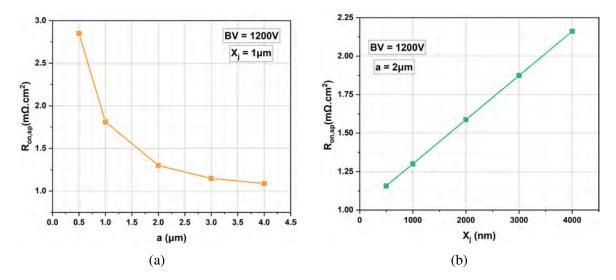

| 3.16 | Total device resistance $R_{on,sp}$ plotted for different (a) JFET region lengths                                                                      |    |

|      | $(x_j)$ and (b) Mesa Widths as calculated by the analytical model presented in                                                                         |    |

|      | Chapter 2. Lengthening and narrowing the JFET region causes $R_{JFET}$ , and                                                                           |    |

|      | therefore $R_{on,sp}$ to increase                                                                                                                      | 63 |

| 3.17 | Current density profile for design B at $V_d$ = 1V, $V_g$ = 0V. The highest current                                                                    |    |

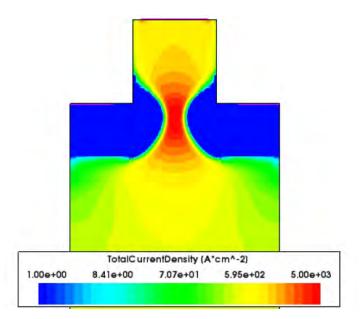

|      | density it found in the centre of the JFET channel region                                                                                              | 64 |

| 3.18 | Output characteristics at $V_g$ = 0V of each of the four designs, showing $R_{on,sp}$                                                                  |    |

|      | increasing with channel length                                                                                                                         | 64 |

xviii List of figures

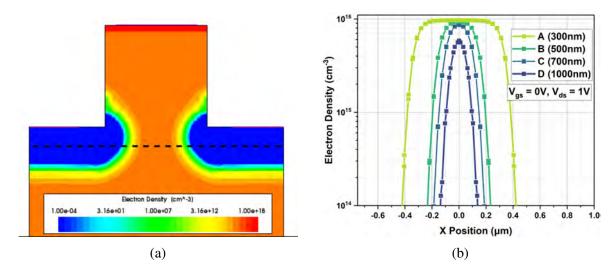

| 3.19 | (a) 2D electron density of design A at $V_g = 0$ V, $V_d = 1$ V, with the position             |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | of a horizontal cut-line shown by a black dashed line (b) Electron density                     |    |

|      | along the horizontal cut-line for all four designs. As channel length increases,               |    |

|      | elevated lateral straggling results in a narrower channel width                                | 65 |

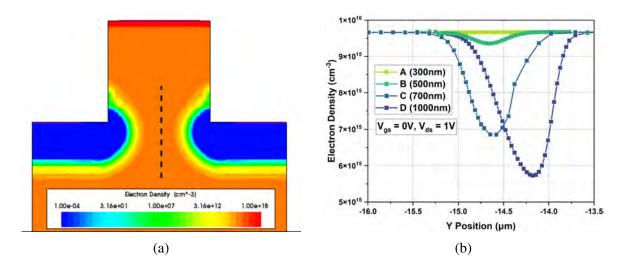

| 3.20 | (a) 2D electron density of design A at $V_d$ = 1V, with the position of a vertical             |    |

|      | cut-line shown by a black dashed line (b) Electron density along the vertical                  |    |

|      | cut-line for all four designs. Longer channel lengths experience partial                       |    |

|      | depletion in the centre of the channel, with the 1000nm long channel having                    |    |

|      | ≤60% of the electron concentration of a 300nm channel                                          | 66 |

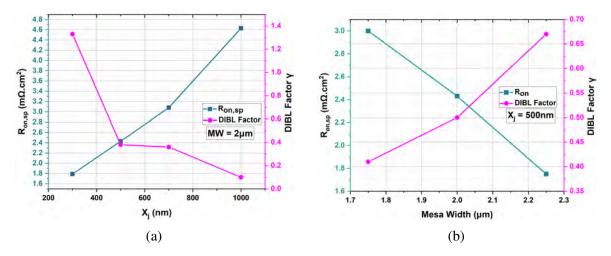

| 3.21 | Specific on-resistance and calculated DIBL factor plotted as a function of (a)                 |    |

|      | junction depth and (b) mesa width. Deeper junctions, and narrower mesas                        |    |

|      | result in a reduced DIBL effect, but at the cost of higher $R_{on,sp}$                         | 67 |

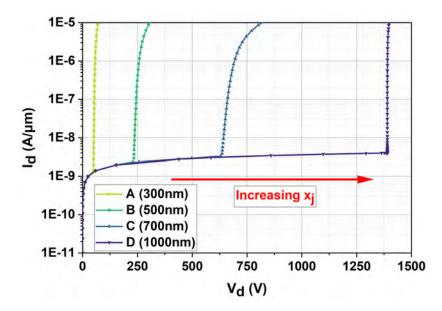

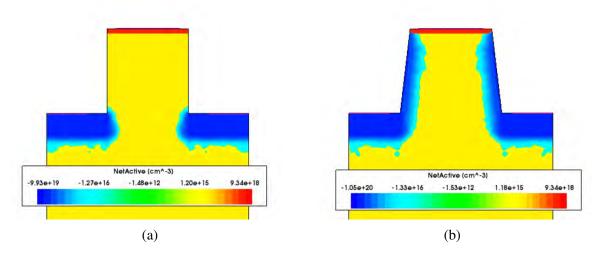

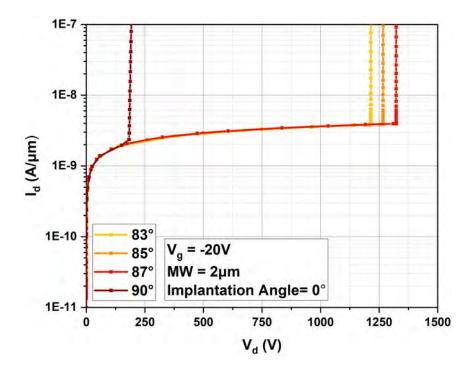

| 3.22 | Breakdown characteristics for each design tested at $V_g$ = -20V, with break-                  |    |

|      | down voltage increasing with junction depth. As junction depth and thus                        |    |

|      | channel length increases, breakdown voltage significantly improves to 1390V                    |    |

|      | for 1000nm                                                                                     | 68 |

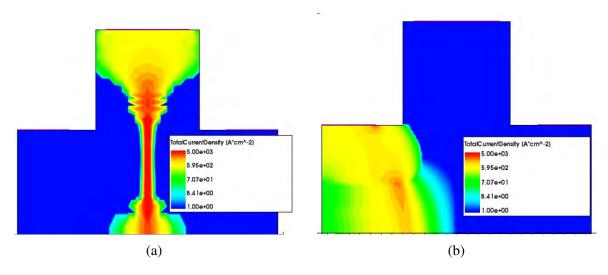

| 3.23 | Two dimensional current density profile at the point of breakdown for (a)                      |    |

|      | Design A (300nm) showing a current path established between the source                         |    |

|      | and drain electrodes, and (b) Design D (1000nm) showing a current path                         |    |

|      | between the gate and drain electrodes through the gate PN junction                             | 68 |

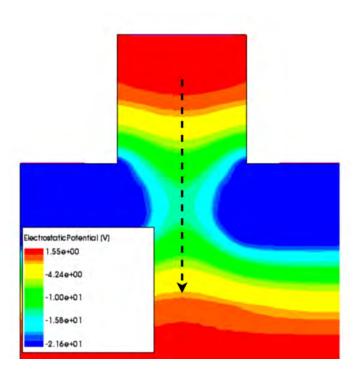

| 3.24 | Cross-section of the electrostatic potential profile of design D (1000nm) at                   |    |

|      | $V_g$ =-20V, $V_d$ = 0V. The position of the vertical cut-line is indicated by an arrow.       | 69 |

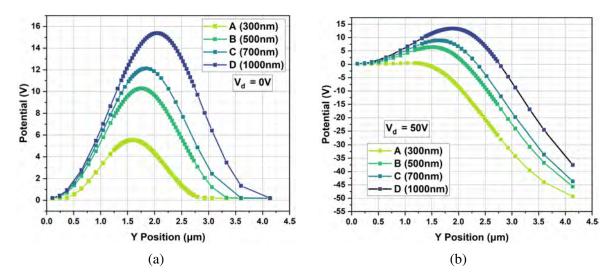

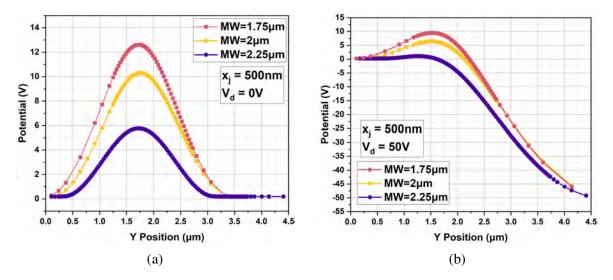

| 3.25 | Potential barrier height in the centre of the channel region $V_g$ = -20V with (a)             |    |

|      | $V_d$ = 0V and (b) $V_d$ = 50V for all four designs. As channel length increases,              |    |

|      | initial barrier height is larger, and experiences less reduction due to DIBL                   |    |

|      | when $V_d$ rises                                                                               | 70 |

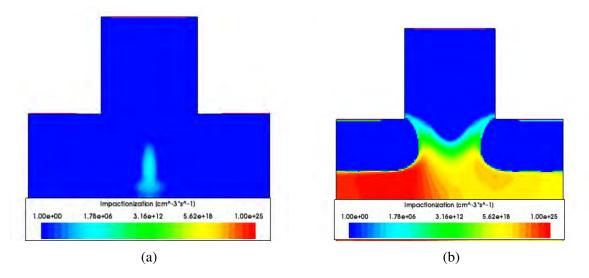

| 3.26 | Electron-hole pair generation rates at the point of breakdown for (a) Design                   |    |

|      | A and (b) Design D. Design A has a very low impact ionization rate, in-                        |    |

|      | dicating that avalanche generation of carriers has not occurred. Design D                      |    |

|      | has a significant impact ionization rate of $5 \times 10^{23} cm^{-3} s^{-1}$ , verifying that |    |

|      | avalanche breakdown has occurred                                                               | 70 |

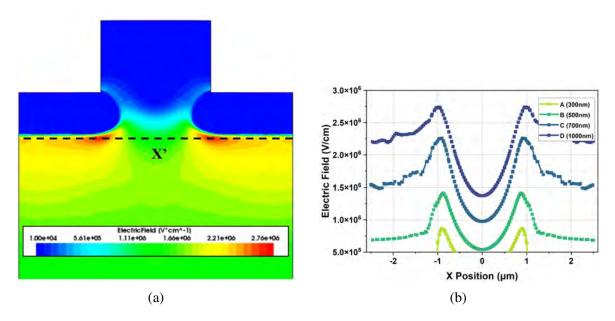

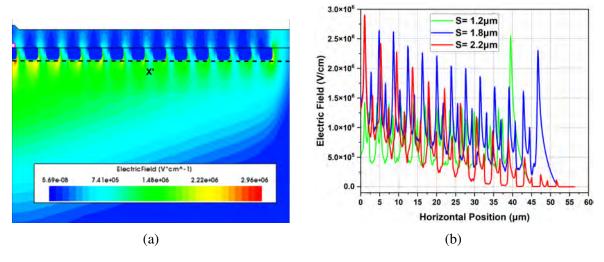

| 3.27 | (a) Electric field profile of design D, indicating the position of a cut-line X'               |    |

|      | (b) Electric field magnitude along cut-line X' for designs A,B,C and D at                      |    |

|      | their respective breakdown voltages. The peak electric field in the designs                    |    |

|      | A, B and C is below the expected $E_c$ of 2.8MV/cm, further verifying that                     |    |

|      | avalanche breakdown has not occurred for these short channel devices                           | 71 |

List of figures xix

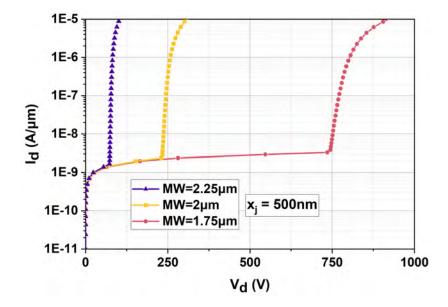

| 3.28 | Breakdown characteristics for design B with varying mesa widths between              |    |

|------|--------------------------------------------------------------------------------------|----|

|      | $1.75\mu m$ to $2.25\mu m$ . Breakdown voltage increases at smaller mesa widths      |    |

|      | as the initial potential barrier height is increased. Breakdown voltage for          |    |

|      | MW= $1.75\mu$ m is only 735V, which indicates that DIBL induced failure is           |    |

|      | still occurring.                                                                     | 72 |

| 3.29 | Potential barrier height for design B (500nm) with varying Mesa Width at             |    |

|      | $V_g = -20$ and (a) $V_d = 0$ V, (b) $V_d = 50$ V. Narrowing mesa width results in a |    |

|      | larger potential barrier, which increases the voltage at which the device fails      |    |

|      | between the source and drain electrodes                                              | 73 |

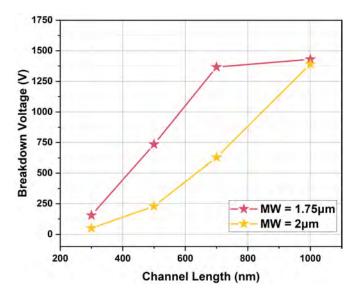

| 3.30 | JFET breakdown voltage plotted as a function of channel length for MW=1.75 $\mu$ m   |    |

|      | and $2\mu$ m, using the values found in table 3.5. Breakdown voltage increases       |    |

|      | with $x_i$ at a greater rate when MW=1.75 $\mu$ m                                    | 73 |

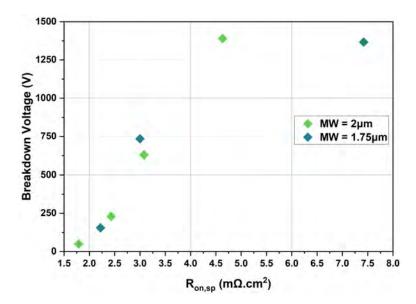

| 3.31 | The trade-off between $R_{on,sp}$ and breakdown voltage for both MW= 1.75 $\mu$ m    |    |

|      | · ·                                                                                  | 74 |

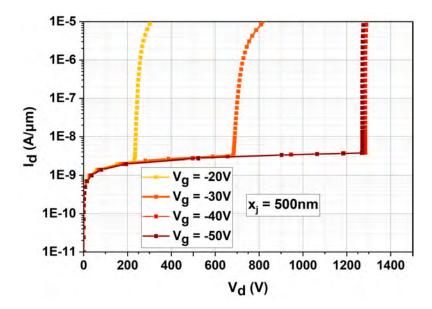

| 3.32 | Breakdown characteristics for design B with varying $V_g$ , with breakdown           |    |

|      | voltage increasing at larger $V_g$ . Breakdown voltage saturates between $V_g$ =     |    |

|      | Ü                                                                                    | 75 |

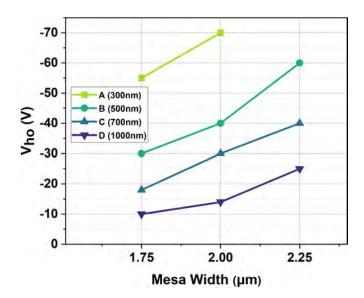

| 3.33 | Hold off voltage plotted for varying mesa width for all four designs, with $V_{ho}$  |    |

|      | reducing at larger $x_i$ . Hold-off voltage is smallest for the 1000nm channel       |    |

|      | with a mesa width of 1.75 $\mu$ m, which is $V_{ho}$ = -10 V                         | 75 |

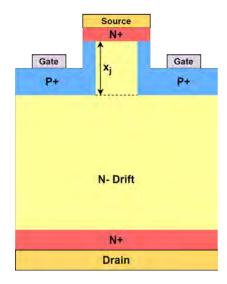

| 3.34 | The cross-section of a JFET unit cell with P-type doping on the mesa sidewall.       |    |

|      | Introducing sidewall doping significantly increases the JFET channel length          |    |

|      |                                                                                      | 77 |

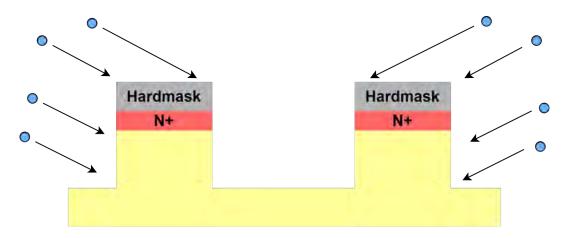

| 3.35 | Visualisation of (a) standard implantation at 0° and (b) sidewall implantation       |    |

|      | at a arbitrary tilt angle. Tilted implantation is required to achieve P-type         |    |

|      | doping on the mesa sidewalls. Additionally, two tilted implantation events           |    |

|      |                                                                                      | 78 |

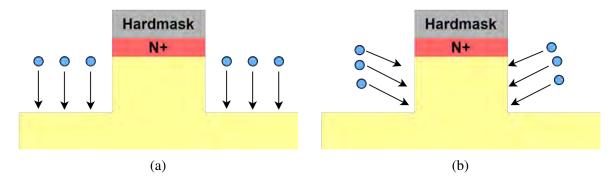

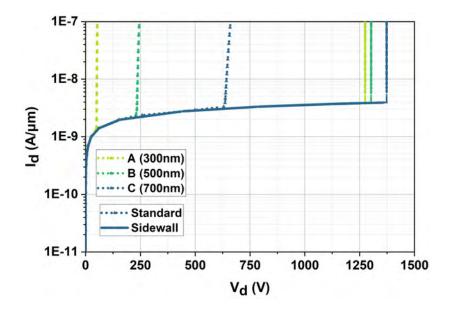

| 3.36 | Comparing all four designs with and without sidewall implantation for (a)            |    |

|      | output characteristics, where sidewall implantation increases $R_{on,sp}$ for all    |    |

|      | designs and (b) transfer characteristics, where $V_{th}$ is shifted significantly    |    |

|      |                                                                                      | 78 |

xx List of figures

| 3.37 | Breakdown performance of designs A,B and C with and without sidewall                 |    |

|------|--------------------------------------------------------------------------------------|----|

|      | implantation. Breakdown voltage increases by over 1000V for a 300nm                  |    |

|      | gate junction depth when sidewall implantation is used. With sidewall p-             |    |

|      | type doping, all designs fail via avalanche rather than DIBL induced punch           |    |

|      | through. The design with a 1000nm junction depth does not experience an              |    |

|      | improvement in BV as it already failed via avalanche, and thus is not shown.         | 79 |

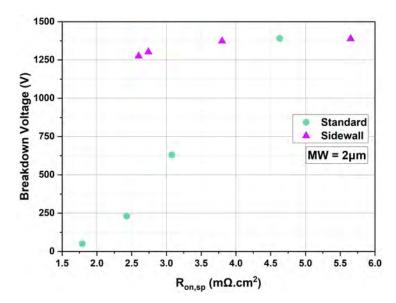

| 3.38 | Trade-off between $R_{on,sp}$ and breakdown voltage for both the sidewall and        |    |

|      | non-sidewall implanted JFETs. By implementing sidewall implantation the              |    |

|      | trade-off is significantly improved                                                  | 80 |

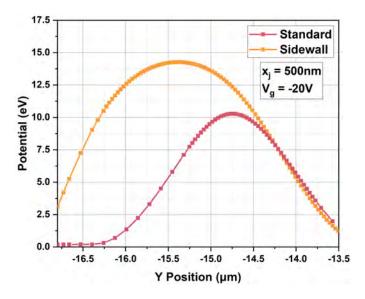

| 3.39 | Potential barrier height of design B at $V_d$ =0V, $V_g$ = -20V. By introducing      |    |

|      | sidewall P-type doping, the potential barrier is larger, and broader                 | 80 |

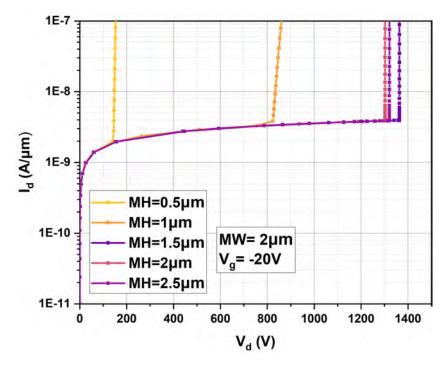

| 3.40 | Breakdown characteristics for the sidewall implanted design B (500nm), with          |    |

|      | varying mesa height. Breakdown voltage significantly reduces when mesa               |    |

|      | height is small because the channel length is reduced                                | 81 |

| 3.41 | Schematic illustration of how adjacent mesas can cause the shadowing effect          |    |

|      | when using tilted implantation                                                       | 82 |

| 3.42 | Schematic visualising coverage of the angled mesa sidewall when using                |    |

|      | standard 0°implantation                                                              | 83 |

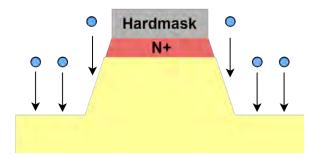

| 3.43 | Doping profiles of design B when using 0°implantation with (a) a 90°sidewall         |    |

|      | (b) a $85^{\circ}$ sidewall                                                          | 83 |

| 3.44 | Breakdown characteristics for standard 0°implantation for different mesa             |    |

|      | sidewall angles. By making the angle acute, P-type coverage of the sidewall          |    |

|      | is achieved with 0° implantation, resulting in a longer channel not affected by      |    |

|      | DIBL                                                                                 | 84 |

| 3.45 | Output characteristics for standard 0°implantation for different sidewall            |    |

|      | angles. Using an acute sidewall angle increases the channel length, which            |    |

|      | increases $R_{on,sp}$                                                                | 84 |

| 3.46 | Doping profile of design B (500nm) JFET edge cell, showing the outer gate            |    |

|      | junction at the extremity of the die                                                 | 86 |

| 3.47 | (a) Electric field profile of the JFET edge cell with an un-terminated gate          |    |

|      | junction at $V_d$ = 450V, showing the location of a horizontal cut-line (b) Electric |    |

|      | field magnitude along the horizontal cut-line, showing a disproportionately          |    |

|      | large peak at the outermost gate junction due to field crowding                      | 86 |

List of figures xxi

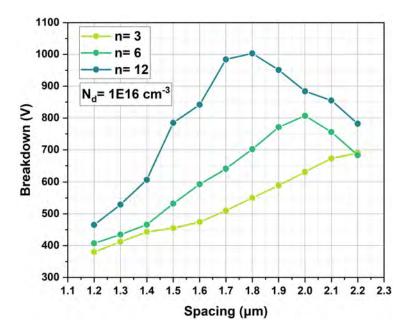

| 3.48        | Breakdown voltage values for the 3,6 and 12 ring designs for the range of                                                       |     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|-----|

|             | spacings between 1.2-2.2 $\mu$ m. The optimum value of S reduces as more rings                                                  |     |

|             | are introduced. The 6 and 12 ring designs exhibit high sensitivity to variation                                                 |     |

|             | in $S$ away from the optimum value                                                                                              | 88  |

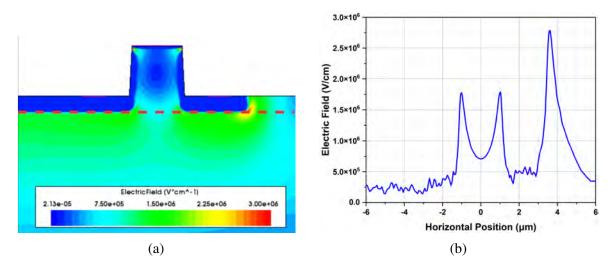

| 3.49        | (a) Electric field profile of $S=1.8\mu m$ at the point of breakdown, with the                                                  |     |

|             | position of the horizontal cut-line X' indicated (b) Electric field magnitude                                                   |     |

|             | along X' at breakdown for $S = 1.2 \mu \text{m}$ , $1.8 \mu \text{m}$ and $2.2 \mu \text{m}$                                    | 89  |

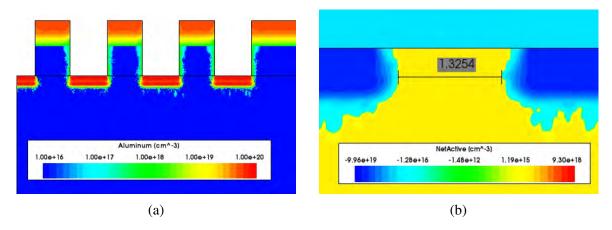

| 3.50        | (a) Aluminium concentration profile post-implantation, showing lateral strag-                                                   |     |

|             | gling under the masking material (b) measured spacing of $1.3\mu m$ between                                                     |     |

|             | the adjacent floating field rings for a designed spacing of $2\mu$ m                                                            | 90  |

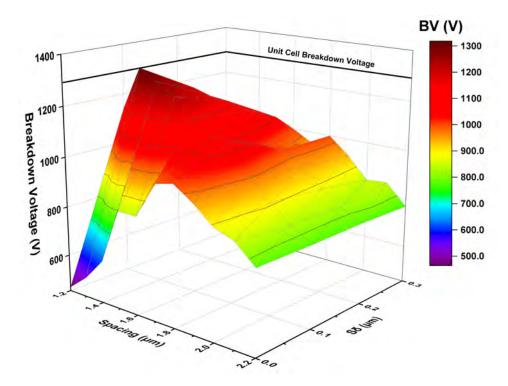

| 3.51        | A heat-map for the 12 FFR design, plotting initial and incremental spacing                                                      |     |

|             | with breakdown voltage. Optimum combinations are found at smaller values                                                        |     |

|             | of S, with $S_{\delta}=0.1\mu$ m                                                                                                | 90  |

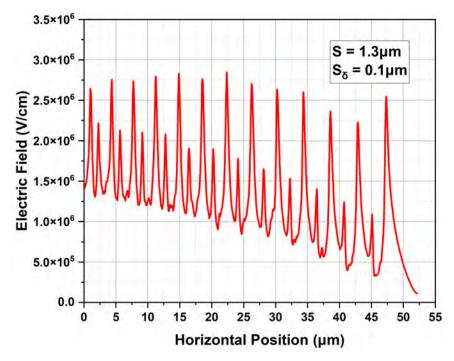

| 3.52        | Electric field profile along horizontal cut-line X' for the optimum combina-                                                    |     |

|             | tion of $S=1.3\mu\text{m}$ , $S_{\delta}=0.1\mu\text{m}$                                                                        | 91  |

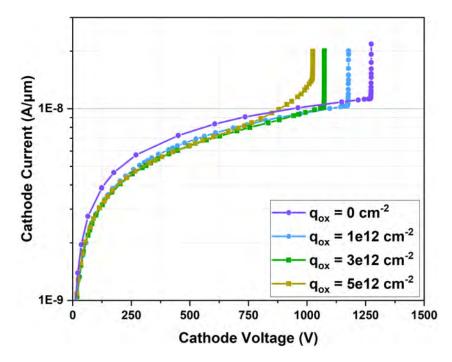

| 3.53        | Breakdown characteristics for the $S=1.4\mu\text{m}$ , $S_{\delta}=0.1\mu\text{m}$ design with varying                          |     |

|             | positive fixed charge at the $SiC/SiO_2$ interface. Breakdown voltage reduces                                                   |     |

|             | as positive charge increases                                                                                                    | 92  |

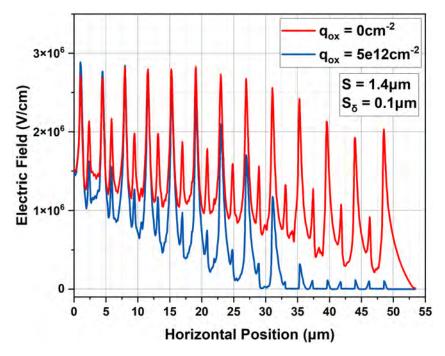

| 3.54        | Electric field magnitude along the horziontal cut-line X' for the $S=1.4\mu m$ ,                                                |     |

|             | $S_{\delta} = 0.1 \mu \text{m}$ design with $q_{ox} = 0 \text{cm}^{-2}$ and $5 \times 10^{12} \text{cm}^{-2}$ . Introduction of |     |

|             | positive fixed charge causes the outer most rings to not support electric field                                                 |     |

|             | equally                                                                                                                         | 93  |

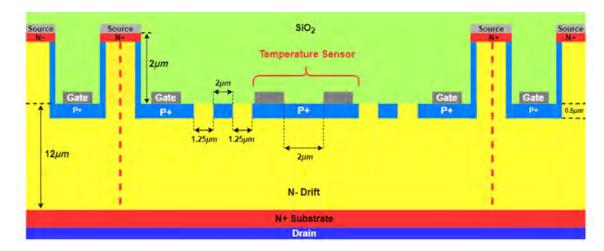

| 4.1         | Doping Profile of the proposed integrated temperature sensor utilising a P-                                                     |     |

| 4.1         | type resistor. Active JFET unit cells are shown bordering the sensing element                                                   |     |

|             | to show how the sensor may be integrated within a JFET stripe architecture.                                                     |     |

|             | A FFR is also on included each side of the sensor. The area simulated in this                                                   |     |

|             | work is indicated by the red dashed lines                                                                                       | 99  |

| 4.2         | Outline of the proposed process flow to form the JFET gate, FFR termination                                                     | 77  |

| <b>⊣.</b> ∠ | and sensor electrode simultaneously. The contact etch opening for the gate                                                      |     |

|             | and sensor pads occurs in the third dimension, and as such is not shown.                                                        |     |

|             | Additionally, the full edge termination which is also formed concurrently is                                                    |     |

|             | not shown.                                                                                                                      | 100 |

| 4.3         | Close up schematic of the integrated temperature sensor, indicating the bias                                                    | 100 |

|             | which should be applied at each sensor contact                                                                                  | 101 |

|             |                                                                                                                                 |     |

**Example 2** List of figures

| 4.4  | Active doping concentration plotted as a function of temperature, for $N_a$ val-               |     |

|------|------------------------------------------------------------------------------------------------|-----|

|      | ues between $10^{17} cm^{-3}$ to $10^{19} cm^{-3}$ . Active doping concentration increases     |     |

|      | with temperature, before beginning to saturate around 500K. This saturation                    |     |

|      | effect is more significant in lower $N_a$ values                                               | 103 |

| 4.5  | Hole mobility plotted as a function of temperature, for $N_a$ values between                   |     |

|      | $10^{17} cm^{-3}$ to $10^{19} cm^{-3}$ . Hole mobility reduces as temperature rises. This      |     |

|      | effect is more significant for lower $N_a$ values                                              | 104 |

| 4.6  | P-type Resistivity plotted as a function of temperature, for $N_a$ values between              |     |

|      | $10^{17} cm^{-3}$ to $10^{19} cm^{-3}$ . Resistivity initially decreases, before saturating    |     |

|      | around 450K. For low values of $N_a$ , the resistivity begins to increase above                |     |

|      | 450K, whilst for $N_a \ge 5 \times 10^{18} cm^{-3}$ the resistivity stays relatively constant. | 105 |

| 4.7  | Doping profile of the lateral P-type sensor that was used to verify in Synopsys                |     |

|      | TCAD simulations to validate and compare to the first principles resistance                    |     |

|      | model                                                                                          | 106 |

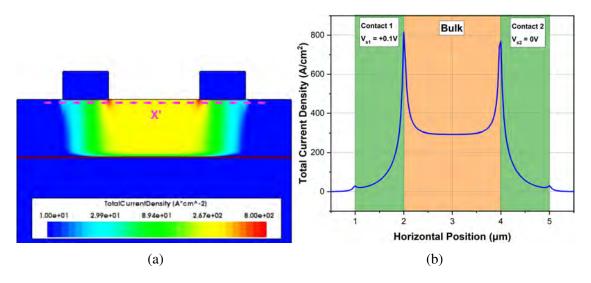

| 4.8  | (a) The 2D current density profile of the lateral P-type sensor at $V_{s1}$ = 0.1V (b)         |     |

|      | Current density magnitude along the horizontal X' cut-line. Current density                    |     |

|      | is highest at the inner edges of both contacts                                                 | 107 |

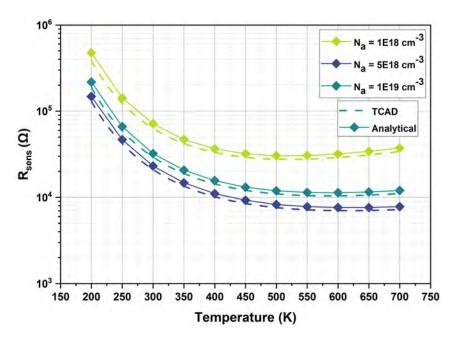

| 4.9  | Comparison between sensor resistance values obtained from drift-diffusion                      |     |

|      | simulations and those calculated using the first-principles model. The re-                     |     |

|      | sistance values from the first-principles model are within 10% of the drift-                   |     |

|      | diffusion simulation results across all tested temperatures                                    | 108 |

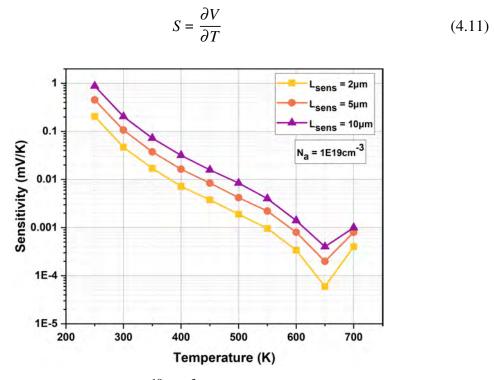

| 4.10 | Sensitivity of the $N_a=1 \times 10^{19} cm^{-3}$ design with different sensor lengths. Due    |     |

|      | to saturation of the incomplete ionization effect, S is close to 0 mV/K above                  |     |

|      | 400K                                                                                           | 109 |

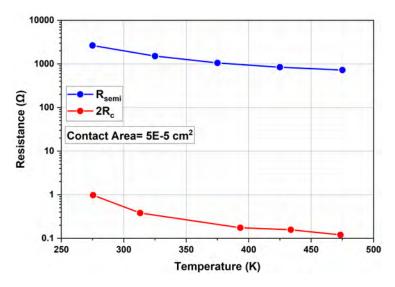

| 4.11 | Comparison between total contact resistance $(2R_c)$ and $R_{semi}$ between 275-               |     |

|      | 475K, using experimentally extracted $\rho_c$ values by Yu et al. Total contact                |     |

|      | resistance is less than 1% of the total resistance at all temperatures                         | 110 |

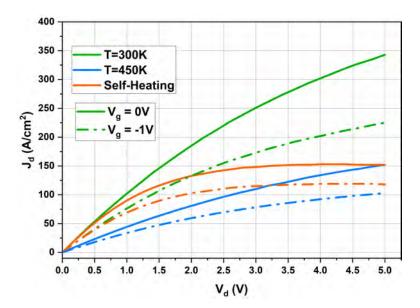

| 4.12 | Comparison between JFET output characteristics considering device self-                        |     |

|      | heating, and at fixed temperatures of 300K and 450K for $V_g$ = 0V, -1V. Device                |     |

|      | self-heating at high power results in a more distinct saturation region                        | 112 |

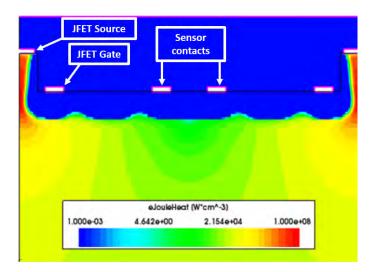

| 4.13 | Electron joule heat profile of the JFET at $V_d$ = 5V, $V_g$ = 0V under self-heating           |     |

|      | conditions. The areas of highest heat generation are the JFET channel regions.                 | 112 |

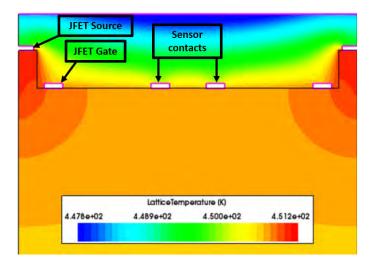

| 4.14 | Temperature profile of the JFET at $V_d$ = 5V, $V_g$ = 0V under self-heating condi-            |     |

|      | tions. The highest temperature is located in the JFET channels, which agrees                   |     |

|      | with the electron joule heat profile. The lattice temperature of the sensor is                 |     |

|      | within 1K of the JFET channels                                                                 | 113 |

List of figures xxiii

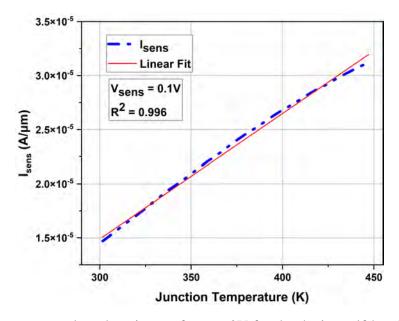

| 4.15       | Sensor current plotted against $T_j$ for $V_g = 0$ V for the device self-heating                                |     |

|------------|-----------------------------------------------------------------------------------------------------------------|-----|

|            | simulation, with a linear fit superimposed. The sensor current is highly linear                                 |     |

|            | with $R^2$ =0.996                                                                                               | 113 |

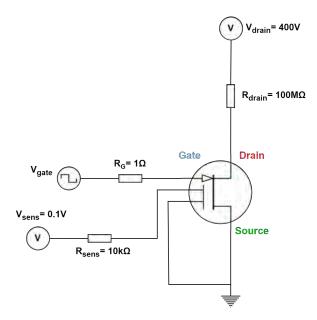

| 4.16       | Equivalent circuit which is used in transient simulation of the JFET with an                                    |     |

|            | integrated sensor. The gate voltage is modelled as a square wave, with a $1\mu$ s                               |     |

|            |                                                                                                                 | 115 |

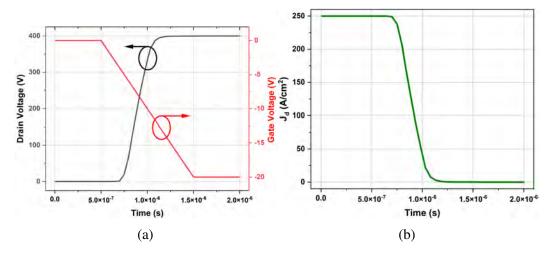

| 4.17       | (a) Gate and drain voltage and (b) drain current density during JFET turn-off.                                  | 115 |

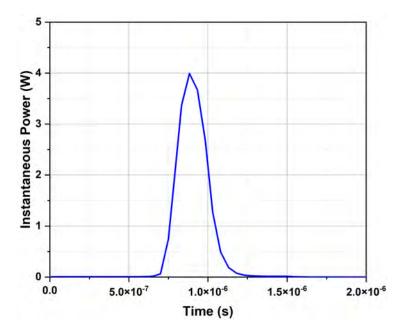

|            | Instantaneous power during the JFET turn-off simulation. Maximum power                                          |     |

|            | was 3.99W at $0.88\mu$ s                                                                                        | 116 |

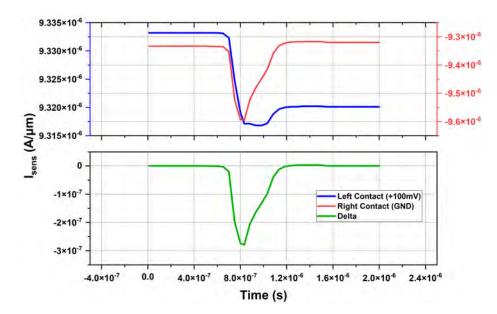

| 4.19       | Current simulated at both sensor contacts during the JFET turn-off. The                                         |     |

|            | discrepancy between the current at each contact is plotted as "Delta". A                                        |     |

|            | negative spike in current is measured at both sensor contacts during the                                        |     |

|            | switching event.                                                                                                | 117 |

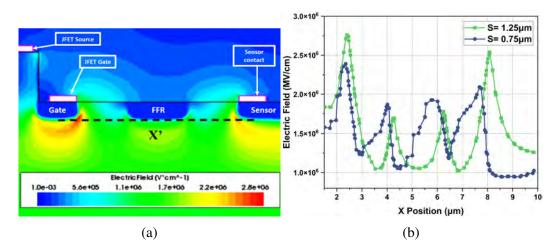

| 4.20       | (a) Electric field profile of the gate, FFR and left hand side of the sensor                                    |     |

|            | contact for $S = 1.25 \mu m$ at the point of breakdown, showing the position of                                 |     |

|            | cut-line X' (b) Electric field magnitude along cut-line X' for $S = 0.75$ and                                   |     |

|            | $1.25\mu m$ . The larger spacing results in a larger peak electric field at the gate                            |     |

|            | and sensor junctions, indicating the spacing is unoptimised                                                     | 118 |

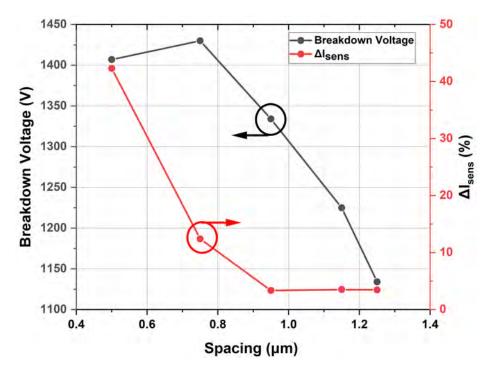

| 4.21       | Breakdown voltage and the reduction in $I_{sens}$ between $V_d$ = 0V and 1000V                                  |     |

|            | $(\Delta I_{sens})$ are plotted as a function of S between $S = 0.5 \mu \text{m}$ and $S = 1.25 \mu \text{m}$ . |     |

|            | Breakdown voltage and $\Delta I_{sens}$ reduce as $S$ increases                                                 | 119 |

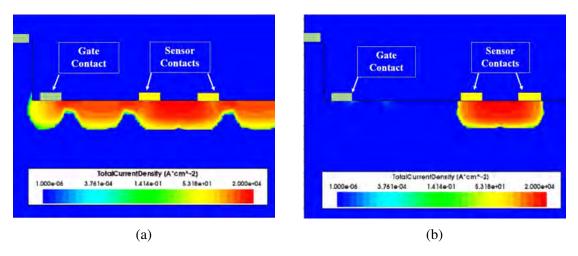

| 4.22       | Total current density at $V_g$ = -20V, $V_d$ = 100V for (a) $S$ = 0.5 $\mu$ m, showing                          |     |

|            | significant current flow between the gate and sensor junctions and (b) $S =$                                    |     |

|            | $1.25\mu m$ with far little to no current flow                                                                  | 119 |

| <b>7</b> 1 |                                                                                                                 |     |

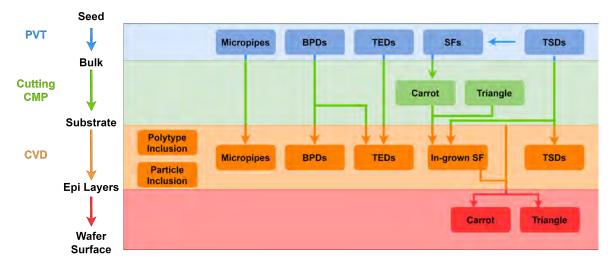

| 5.1        | Schematic of which step of SiC wafer manufacturing different material                                           |     |

|            | defects originate from. Arrows indicate how defects can propagate in subse-                                     | 104 |

| <i>7</i> 2 | quent manufacturing processes                                                                                   | 124 |

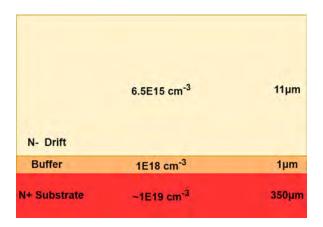

| 5.2        | Epitaxial structure of SiC wafers used for defect study. The N-drift region                                     |     |

|            | is $11\mu$ m thick, with a doping concentration of $N_d$ =6.5 × $10^{15}$ cm <sup>-3</sup> . The                | 107 |

| <i>7</i> 2 | substrate thickness is $350\mu \text{m}$                                                                        | 127 |

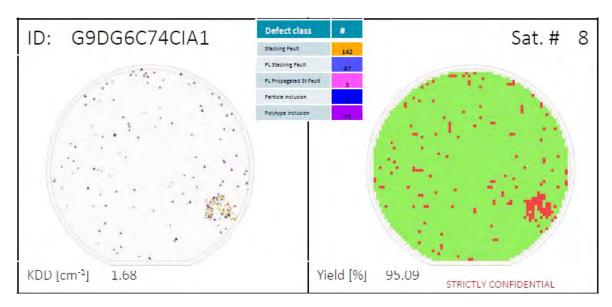

| 5.3        | Wafer Map of defect locations for WAF1 using a Lasertec SICA tool. The                                          |     |

|            | left hand side displays the location of the different type of defects, whilst the                               |     |

|            | right shows yield of the wafer. The highest concentration of defects is in the                                  | 100 |

|            | bottom right hand corner of the wafer                                                                           | 128 |

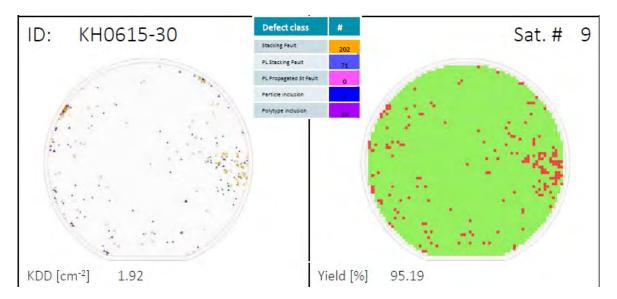

**xxiv** List of figures

| 5.4  | Wafer Map of defect locations for WAF2 using a Lasertec SICA tool. The right hand side displays the location of the different type of defects, whilst the right shows yield of the wafer. The highest concentration of defects is |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | found in the middle right hand side of the wafer                                                                                                                                                                                  | 128 |

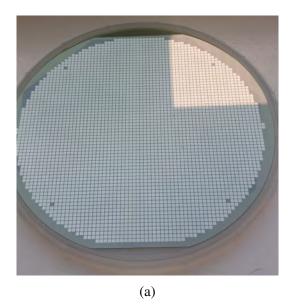

| 5.5  | Electrical test setup consisting of a Wentworth S200FA semi-automated                                                                                                                                                             |     |

| 5.6  | probe station (left) and a Keysight B1505A Power Device Analyser (centre). (a) Wafer 1 after fabrication of SBDs has been completed. (b) Corresponding wafer map of the wafer generated on the S200FA software for automated      | 129 |

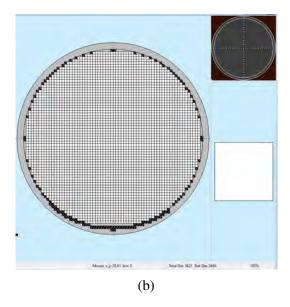

|      | testing program.                                                                                                                                                                                                                  | 130 |

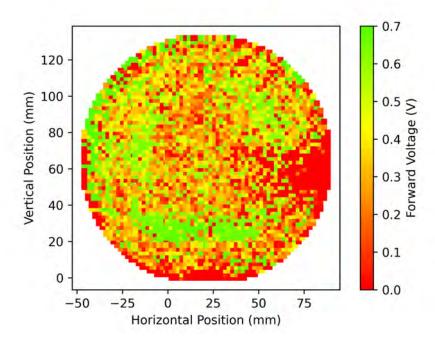

| 5.7  | Heat-map of forward voltage across WAF1. A significant proportion of diodes have $V_f$ of near 0V, indicating that they are suffering from high                                                                                   |     |

|      | leakage current, and are likely defective.                                                                                                                                                                                        | 133 |

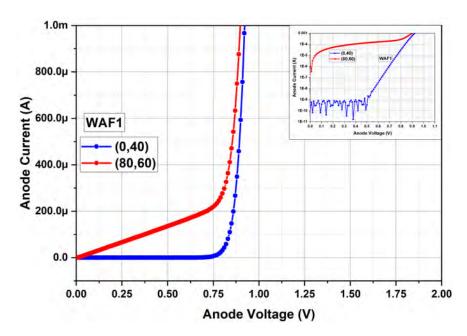

| 5.8  | Comparison between the diodes found at positions (0,26) and (80,60) on                                                                                                                                                            |     |

|      | WAF1. Diode (80,60) conducts $I_a \ge 0.1 \mu$ A immediately, whilst diode (0,26)                                                                                                                                                 |     |

|      | begins conducting current 0.55V. This indicates that diode (80,60) is not                                                                                                                                                         |     |

|      | behaving as a SBD, and is defective                                                                                                                                                                                               | 134 |

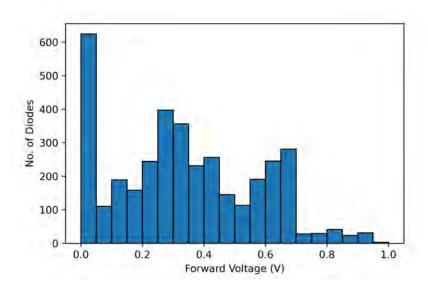

| 5.9  | Distribution of $V_f$ at $I_a$ = 1 $\mu$ A across WAF1. Over 600 diodes have $V_f$ values                                                                                                                                         |     |

|      | of near 0V, indicating that they suffer from the same forward leakage issues                                                                                                                                                      |     |

|      | as diode (80,60)                                                                                                                                                                                                                  | 135 |

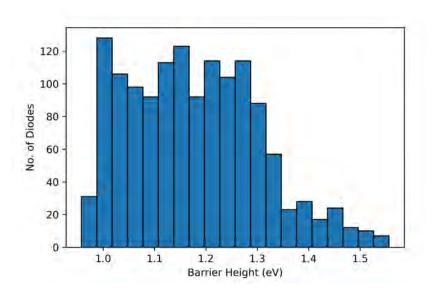

| 5.10 | Distribution of $\phi_b$ across WAF1 for the remaining acceptable 1381 diodes. The average $\phi_b$ was found to be 1.18eV, with a minimum of 0.95eV                                                                              | 136 |

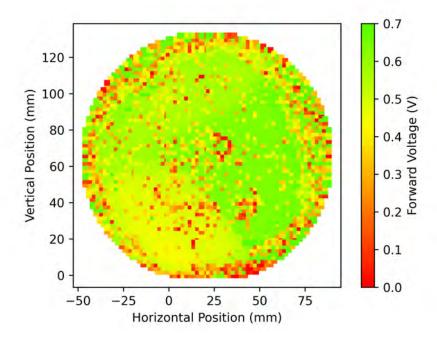

| 5.11 | Heat-map of $V_f$ across wafer 2. Far fewer diodes exhibit a $V_f$ close to 0V                                                                                                                                                    |     |

|      | compared to WAF1. The diodes located in bottom-left quadrant of the wafer                                                                                                                                                         |     |

|      | have a lower $V_f$                                                                                                                                                                                                                | 137 |

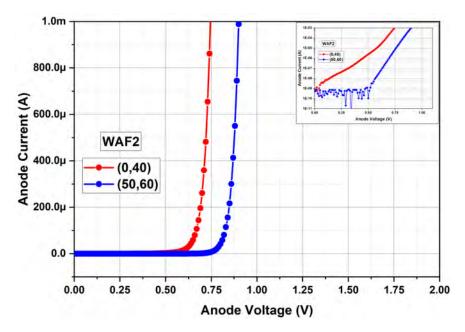

| 5.12 | Comparison of the forward characteristics of diodes (0,40) and (50,60) on                                                                                                                                                         |     |

|      | wafer 2. Diode (0,40) has a $V_f$ of 0.32V, whilst for diode (50,60) $V_f$ = 0.64V.                                                                                                                                               |     |

|      | Anode current for diode (0,40) begins increasing almost exponentially at low                                                                                                                                                      |     |

|      | $V_a$                                                                                                                                                                                                                             | 138 |

| 5.13 | Distribution of $V_f$ across WAF2. The majority of diodes on the wafer had $V_f$                                                                                                                                                  |     |

|      | values between 0.4-0.7V. The majority of diodes with $V_f$ below 0.4V can be                                                                                                                                                      |     |

|      | found in the bottom-left quadrant of the wafer                                                                                                                                                                                    | 138 |

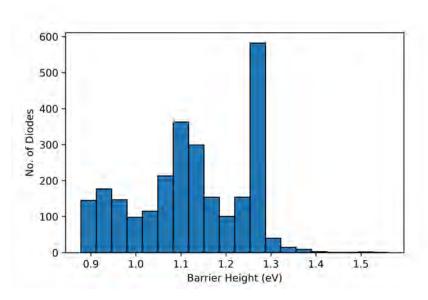

| 5.14 | Distribution of $\phi_b$ across WAF2. The most common $\phi_b$ range was 1.25 -                                                                                                                                                   |     |

|      | 1.29eV, followed by 1.08 - 1.12eV. The average barrier height was 1.12eV.                                                                                                                                                         | 139 |

| 5.15 | Heat-map of breakdown voltage across WAF1. Localised areas of poor                                                                                                                                                                |     |

|      | breakdown are observed on the middle right hand side of the wafer, and in                                                                                                                                                         |     |

|      | the outer devices towards the bottom left                                                                                                                                                                                         | 140 |

List of figures xxv

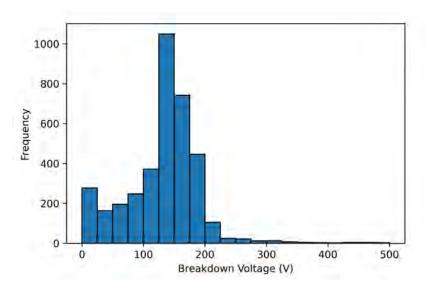

| 5.16 | Distribution of breakdown voltages on WAF1. Most devices failed between               |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | 100-200V. Very few devices sustained voltages above 300V. A significant               |     |

|      | amount of devices failed below 25V                                                    | 141 |

| 5.17 | Comparison between the reverse characteristics of diodes (0,40) and (80,60).          |     |

|      | Diode (0,40) experiences a gradual increase in current from 3nA at 10V to             |     |

|      | 1mA at 160V, compared to diode (80,60) which conducts 1mA by $V_c$ =10V.              | 142 |

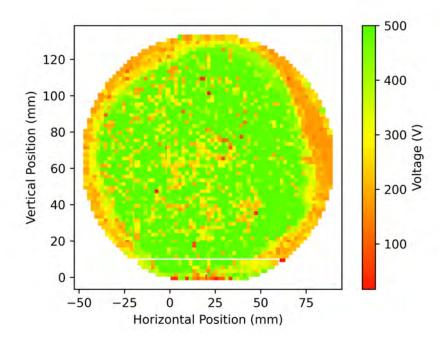

| 5.18 | Heat-map of breakdown voltage across WAF2. Degradation in breakdown                   |     |

|      | voltage is observed around the edges of the wafer. It should be noted that            |     |

|      | the scale on this figure is not equivalent to figure 5.15, where the maximum          |     |

|      | value was 200V                                                                        | 143 |

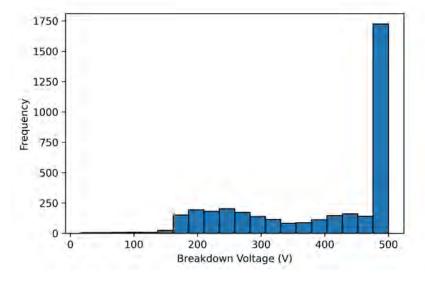

| 5.19 | Distribution of breakdown voltages on WAF2. Almost 50% of diodes did                  |     |

|      | not fail at the maximum voltage of 500V                                               | 143 |

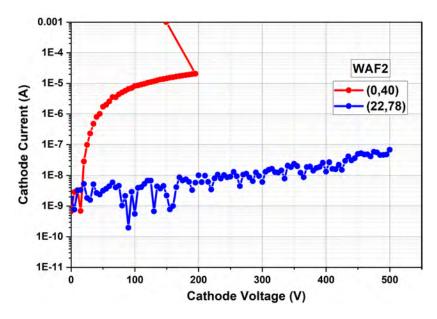

| 5.20 | Reverse characteristics of diodes (0,40) and (22,78). Diode (0,40) has a              |     |

|      | breakdown voltage of 195V, compared to diode (22,78) which has not failed             |     |

|      | when the maximum $V_c$ =500V was applied                                              | 144 |

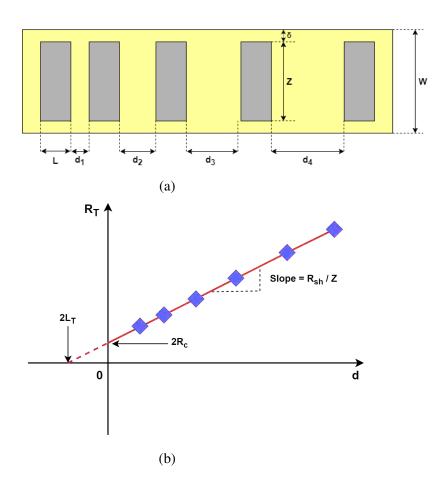

| 6.1  | (a) A standard TLM test structure, with rectangular spaced pads on a highly           |     |

| 0.1  | doped region of semiconductor, separated by incrementally larger distances.           |     |

|      | (b) The corresponding plot of $R_T$ as a function of contact spacing $d$ , illustrat- |     |

|      | ing parameters which may be extracted from the plot                                   | 148 |

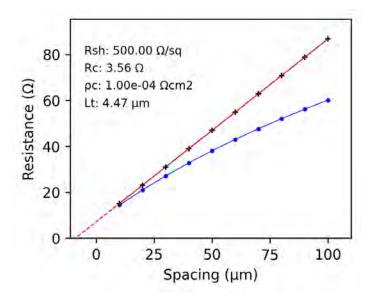

| 6.2  | Circular TLM structures, where the shaded area represents deposited metal,            | 140 |

| 0.2  | and yellow represents bare the bare semiconductor surface                             | 149 |

| 6.3  | Example fit of ideal CTLM data, with uncorrected data shown in blue, and              | 147 |

| 0.5  | corrected data shown in black                                                         | 150 |

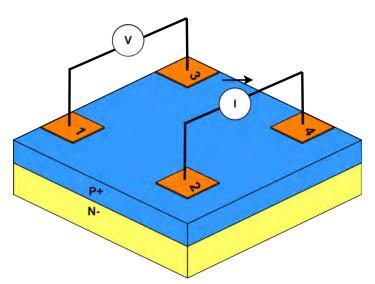

| 6.4  | Diagram of a Van der Pauw structure on a N- epitaxial layer which has been            | 150 |

| 0.4  | implanted with P-type species. Voltage is applied across contacts 1 and 3,            |     |

|      | whilst current is measured between contacts 2 and 4                                   | 151 |

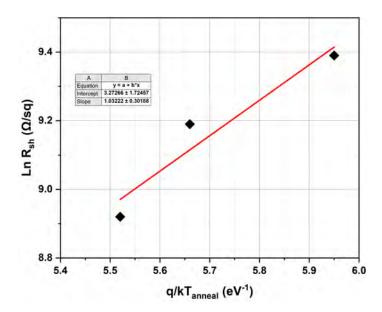

| 6.5  | Arrhenius plot of sheet resistance of an aluminium implanted 4H-SiC layer             | 131 |

| 0.5  | recreated using the data from Spera et al. [1] The extracted $E_{act}$ is 1.03eV.     |     |

|      | $R_{sh}$ reduces at higher activation anneal temperatures                             | 152 |

| 6.6  | Schematic of the Hall effect measurement setup on a Van Der Pauw test                 | 132 |

| 0.0  | structure. Current is applied across contacts 1 and 3, whilst Hall voltage is         |     |

|      | measured between contacts 2 and 4. A magnetic field is applied perpendicular          |     |

|      | to the sample surface                                                                 | 154 |

|      | to the building building.                                                             | 154 |

**xxvi** List of figures

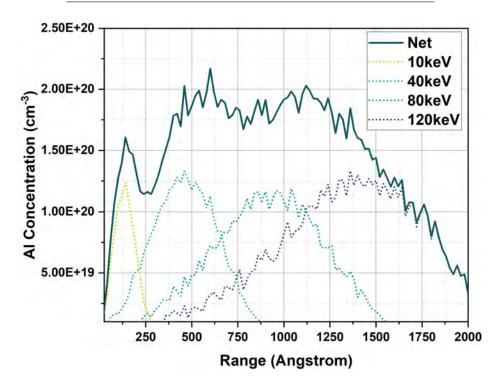

| 6.7  | Photoresist thickness on silicon wafers after hard-bakes at 210°Cof different            |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | lengths. Initially, a significant decrease in PR thickness is observed. After an         |     |

|      | accumulative 30 minute bake, the reduction in thickness begins to saturate at            |     |

|      | 1nm/min                                                                                  | 156 |

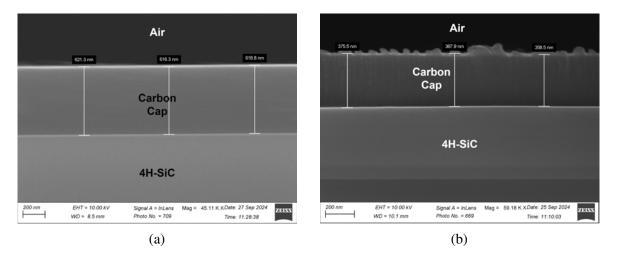

| 6.8  | Cross-sectional SEM image of the carbon cap formed on a silicon substrate                |     |

|      | after the conversion anneal. The average thickness of the layer is 870nm                 | 157 |

| 6.9  | Cross-sectional SEM image of the carbon cap formed on a SiC substrate                    |     |

|      | after the conversion anneal. The average thickness of the layer is 763nm                 | 158 |

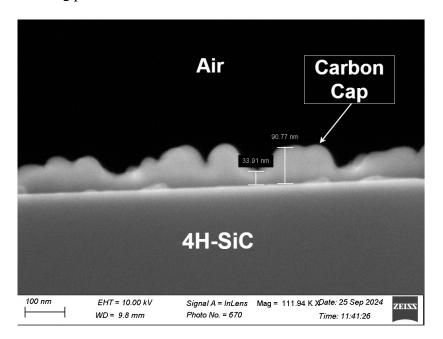

| 6.10 | Cross-sectional SEM images of carbon cap thickness after (a) a 2 minute $O_2$            |     |

|      | plasma and (b) a 5 minute $O_2$ plasma                                                   | 159 |

| 6.11 | Cross-sectional SEM of carbon cap after being subjected to a $O_2$ plasma                |     |

|      | for 10 minutes. Significant variation in thickness is observed. The average              |     |

|      | thickness was found to be 56nm                                                           | 159 |

| 6.12 | (a) Carbon cap thickness plotted as a function of $O_2$ plasma time. The                 |     |

|      | average removal rate is 71 nm/min. (b) Half the 100mm carbon-capped SiC                  |     |

|      | substrate after being subjected to a 10 minute $O_2$ plasma. The layer has been          |     |

|      | completely removed from the extremities of the sample, but is still visible in           |     |

|      | the sample centre.                                                                       | 160 |

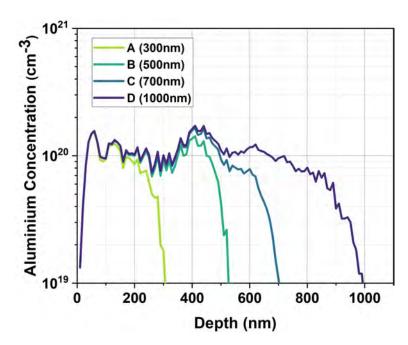

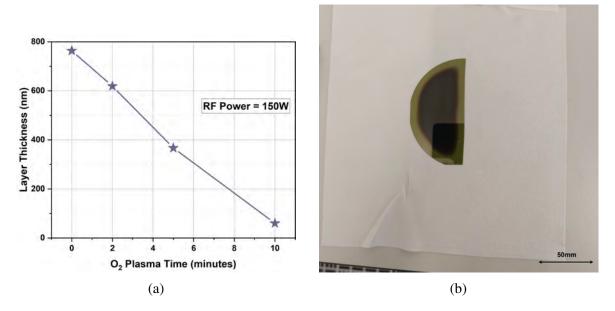

| 6.13 | Resulting simulated aluminium doping profile calculated using SRIM for the               |     |

|      | implant scheme in table 6.1                                                              | 161 |

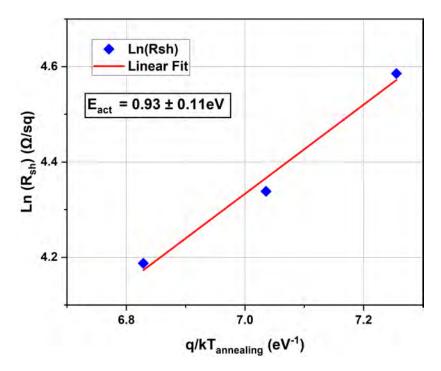

| 6.14 | Arrhenius plot of sheet resistance as a function of activation anneal tempera-           |     |

|      | ture for implanted aluminium P-type. Sheet resistance reduces with $T_{anneal}$ ,        |     |

|      | indicating improved activation of implanted ions                                         | 163 |

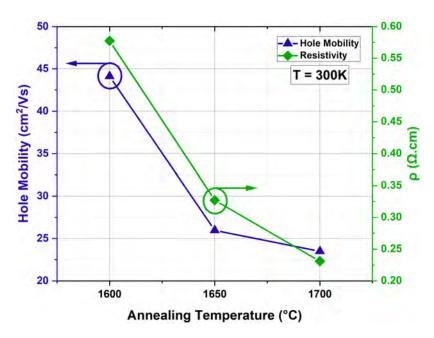

| 6.15 | Resistivity and hole mobility plotted as a function of annealing temperature.            |     |

|      | The reduction in $\mu_p$ and $\rho$ is further supports that more active aluminium       |     |

|      | dopants are present when annealing at higher $T_{anneal}$ temperatures                   | 164 |

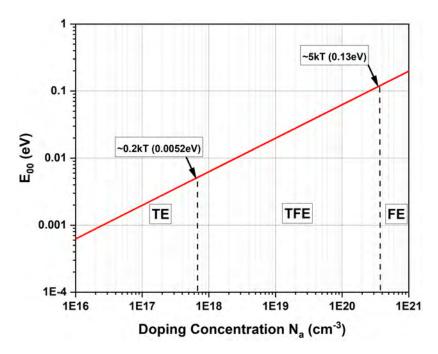

| 6.16 | $E_{00}$ plotted as a function of $N_a$ for 4H-SiC. As doping concentration increases,   |     |

|      | carrier transport by field emission rises. However, for the majority of $N_a$            |     |

|      | values typically used to form ohmic contacts, a mixture of FE and TE is                  |     |

|      | expected to occur (TFE)                                                                  | 165 |

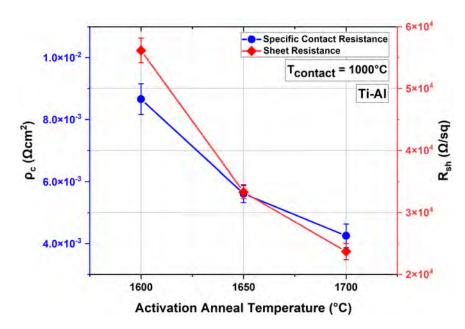

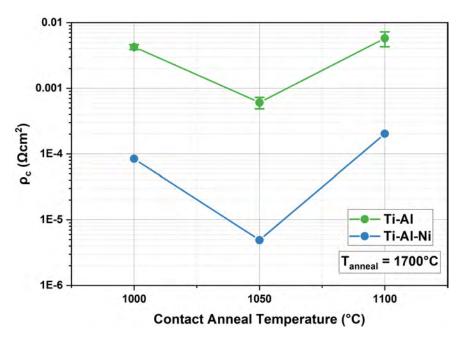

| 6.17 | Sheet resistance and $\rho_c$ plotted as a function of $T_{anneal}$ as calculated from   |     |

|      | CTLM measurements. Both $\rho_c$ and $R_{sh}$ reduce at higher $T_{anneal}$ , indicating |     |

|      | improved activation of aluminium dopants at higher temperatures                          | 166 |

| 6.18 | Specific contact resistance plotted as a function of $T_{contact}$ for both Ti/Al and    |     |

|      | Ti/Al/Ni samples. The Ti/Al/Ni metal stack achieves significantly lower $\rho_c$         |     |

|      | values for all anneal temperatures                                                       | 167 |

List of figures xxvii

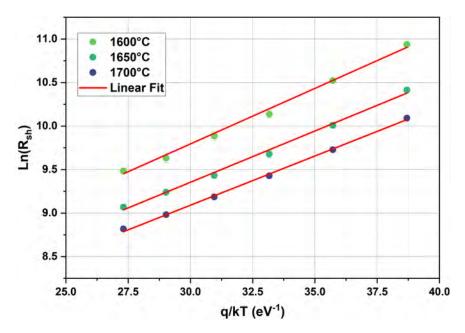

| 6.19 | Arrhenius plots of $R_{sh}$ for each of the three activation anneals. Data from all                                  |     |

|------|----------------------------------------------------------------------------------------------------------------------|-----|

|      | three samples gives a good linear fit. It is found that $E_{ion}$ reduces as $T_{contact}$                           |     |

|      | rises, indicating improved activation of dopants                                                                     | 168 |

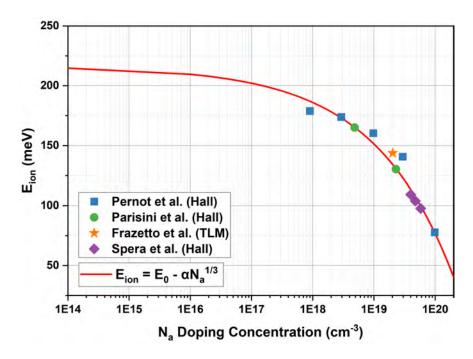

| 6.20 | Ionization energy of aluminium acceptors in 4H-SiC as a function of $N_a$                                            |     |

|      | determined by Hall and TLM measurements from existing literature. The                                                |     |

|      | solid line corresponds to the expression for $E_{ion}$ as a function of $N_a$ which is                               |     |

|      | presented in equation 6.20, using $E_0 = 216 \text{meV}$ and $\alpha = 3 \times 10^{-5} \text{meV} \text{cm}^{-1}$ . | 169 |

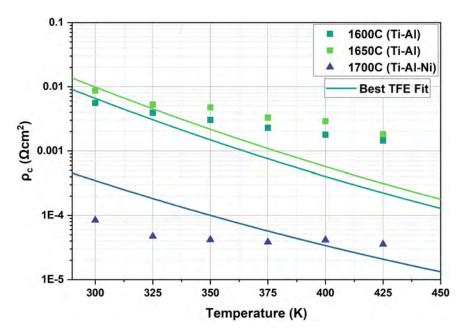

| 6.21 | Specific contact resistance plotted as a function of measurement temperature,                                        |     |

|      | for all three $T_{anneal}$ temperatures. The Thermionic Field Emission equation                                      |     |

|      | is fitted to the data using $N_a$ values from the previous section. The TFE fit                                      |     |

|      | to all three sets of data is poor, indicating that TFE may not be the primary                                        |     |

|      | transport mechanism across the contact                                                                               | 171 |

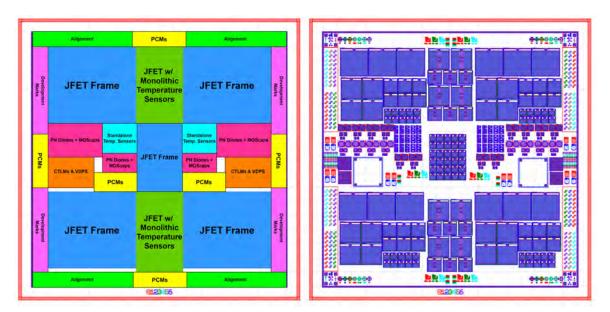

| C.1  | Mask layout designed for the proposed SiC JFET process flow. The left hand                                           |     |

|      | side image indicates which areas contain different device and test structures                                        |     |

|      | across the piece. On the right, the full layout design is displayed                                                  | 209 |

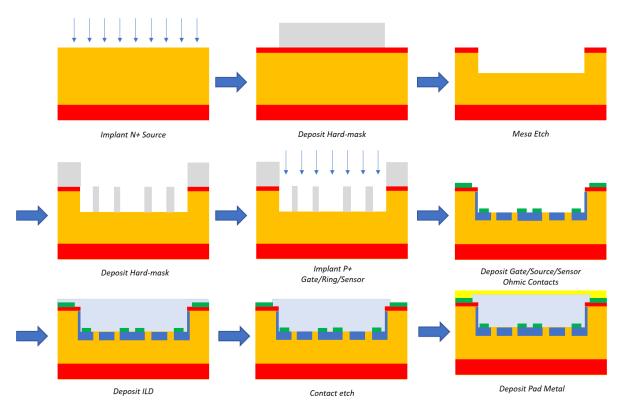

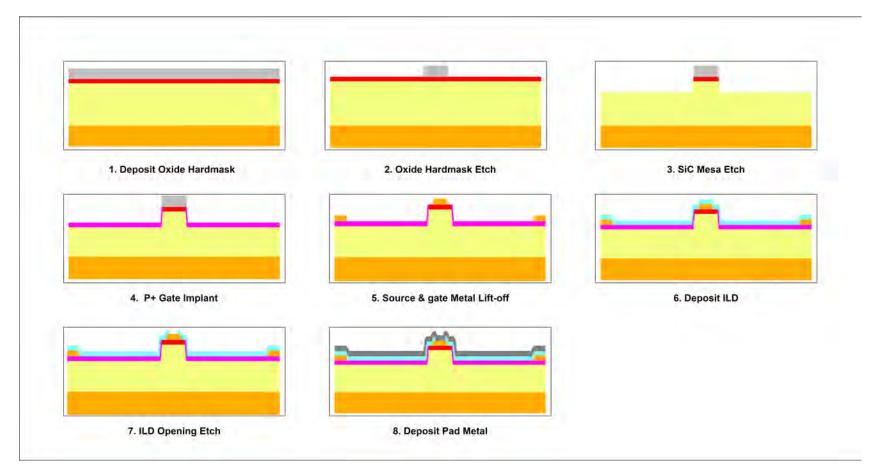

| C.2  | Outline of proposed SiC JFET fabrication process flow. Five individual mask                                          |     |

|      | layers are required for this process: Oxide Hardmask/SiC Mesa Etch, Device                                           |     |

|      | Isolation etch (not shown), Source & Gate contact metal, ILD Opening Etch,                                           |     |

|      | Pad Metal lift off and Passivation etch back (not shown). The isolation etch                                         |     |

|      | and passivation layers are not shown in this flow diagram as they have no                                            |     |

|      | bearing on the unit cell structure of the JFET                                                                       | 211 |

# List of tables

| 1.1  | Comparison of fundamental material properties for silicon, 4H-SiC and GaN.                          | 3  |

|------|-----------------------------------------------------------------------------------------------------|----|

| 2.1  | Dimensions and doping concentrations used for JFET $R_{on,sp}$ model                                | 26 |

| 2.2  | Dimensions and doping concentrations used for HEMT $R_{on,sp}$ model                                | 34 |

| 2.3  | Model parameters for calculating carrier lifetimes                                                  | 40 |

| 2.4  | Parameters used to calculate bandgap energy as a function of temperature,                           |    |

|      | and doping. *n-type **p-type                                                                        | 41 |

| 2.5  | Parameters used in the Okuto-Crowell Impact Ionization Model                                        | 42 |

| 2.6  | Ionization energies for common donor species in 4H-SiC                                              | 44 |

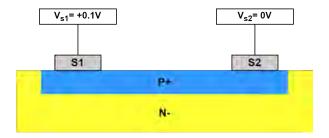

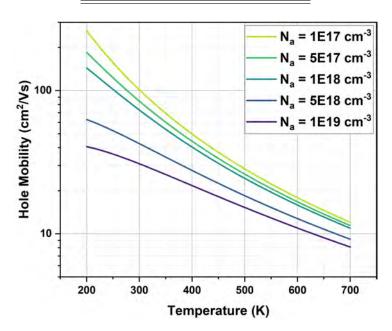

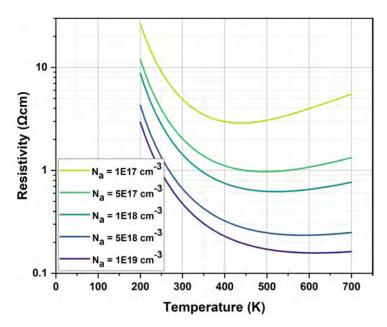

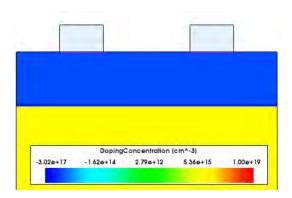

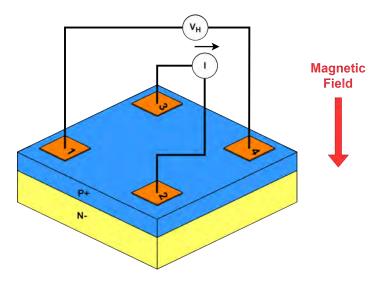

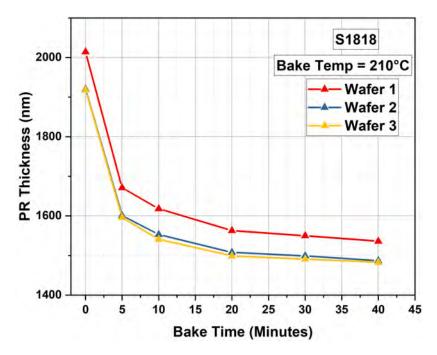

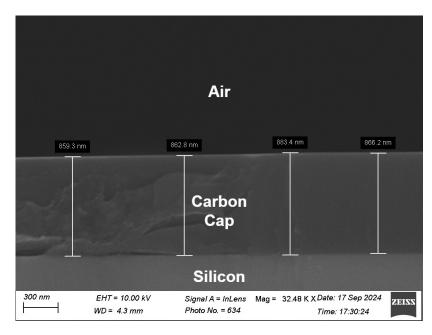

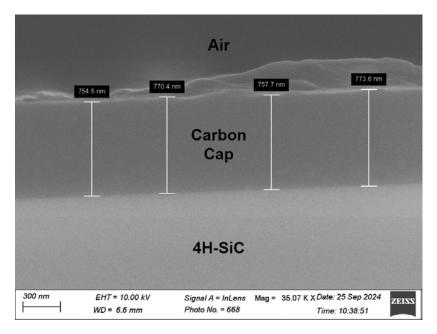

| 2.7  | Ionization energies for common acceptor species in 4H-SiC                                           | 44 |